#### Practice 7:

## **CMOS** Capacitance

Digital Electronic Circuits – Semester A 2012

# **MOSFET** Capacitances

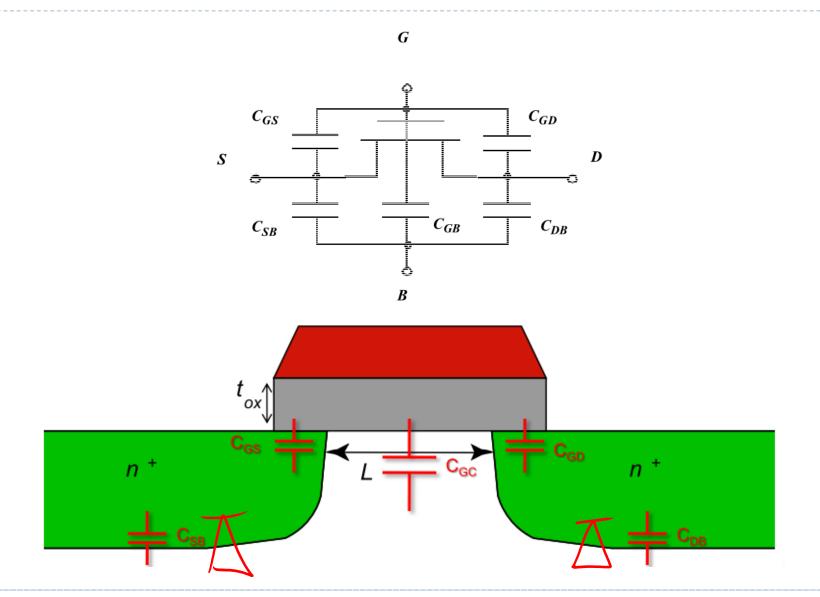

#### **MOSFET** Capacitance Components

### Gate to Channel Capacitance

In general, the gate capacitance is similar to a parallel plate capacitor:

However, what is the other terminal of the gate capacitance?

$= C_{ox} \cdot W \cdot L$

- This is dependent on the existence and characteristics of the channel.

- But we have to attribute the capacitance to one of the electrical terminals (i.e. G, S, D, B) of the transistor.

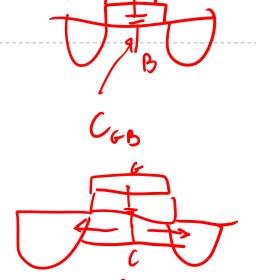

- In *cut-off*, no channel exists.

- All capacitance is to the body:

$$C_{GB} = C_g = \underline{C_{ox}} \cdot W \cdot L$$

$$C_{GS} = C_{GD} = 0$$

- In *linear*, the channel extends across the entire length.

- There is no capacitance to body.

- We attribute half of the gate capacitance to the source and half to the drain.

$$C_{GB} = 0$$

$C_{GS} = C_{GD} = \frac{1}{2}C_g = \frac{1}{2}C_{ox}WL$

### Gate to Channel Capacitance

- In saturation, the channel ends before the drain.

- There is no capacitance to the drain!

- There is still no capacitance to the body.

- > The total capacitance is smaller than the full value.

$$C_{GD} = 0$$

$C_{GB} = 0$   $C_{GS} = \frac{2}{3}C_g = \frac{2}{3}C_{ox} \cdot W \cdot L$

- Velocity saturation does not affect the channel.

- Capacitance components should be calculated according to long channel approximations!

Sat

## **Overlap Capacitances**

- Overlap capacitances exist independently of the channel

- The length of the overlap is deterministic, therefore:

$$C_{GD,overlap} \approx C_{ox} \cdot W \cdot L_{D,overlap} = C_{D,overlap} \cdot W$$

We will assume that the source and drain are equivalent.

In actuality, this is layout dependent.

$$C_{D,overlap} = C_{S,overlap} = C_{ov}$$

## **Diffusion Capacitance**

- Diffusion capacitance is made up of the reverse-bias capacitance of the source and drain diodes.

- This capacitance is voltage dependent and is proportional to the junction area of the diode.

LSW

$$C_{bottom} = C_{j} \cdot W \cdot L_{diff}$$

$$C_{sidewalls} = C_{sw} \left(W + 2L_{diff}\right)$$

$$C_{DB} = C_{SB} = C_{bottom} + C_{sidewalls}$$

#### • We will usually give you this as a pre-calculated capacitance.

| Component                         | Cut-off            | Linear                                            | Saturation              |

|-----------------------------------|--------------------|---------------------------------------------------|-------------------------|

| C <sub>GB</sub>                   | C <sub>ox</sub> WL | 0                                                 | 0                       |

| C <sub>GS</sub>                   | C <sub>ov</sub> W  | $\underbrace{0.5C_{ox}WL} + \underbrace{C_{ov}W}$ | $2/3C_{ox}WL + C_{ov}W$ |

| C <sub>GD</sub>                   | C <sub>ov</sub> W  | $0.5C_{ox}WL + C_{ov}W$                           | C <sub>ov</sub> W       |

| C <sub>DS</sub> , C <sub>DB</sub> | C <sub>diff</sub>  | C <sub>diff</sub>                                 | C <sub>diff</sub>       |

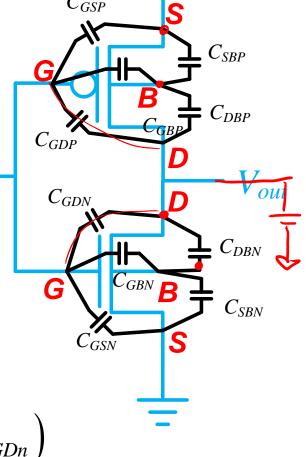

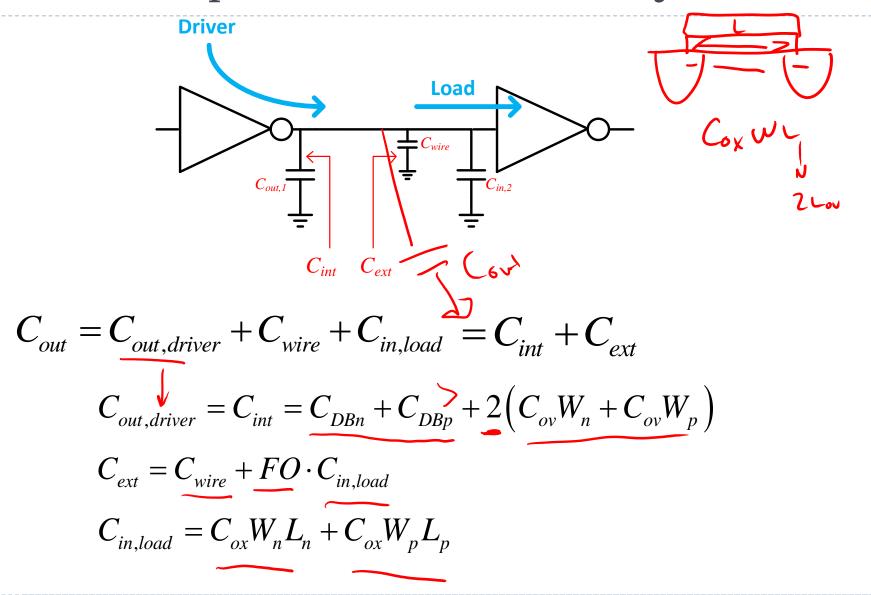

## **CMOS** Inverter Capacitances

### Delay Capacitance Assumptions

- We would like to estimate the capacitance of a CMOS stage for propagation delay calculation  $(t_{pd}=0.69RC)$

- We only care about the relevant capacitance during the 50% transition!

- To make things easier, we will assume all capacitances are to Ground and <u>lump</u> them together:

$$C_{out} = C_{out,driver} + C_{wire} + C_{in,load}$$

$$= C_{int} + C_{ext}$$

$$C_{out,driver} = C_{int} + C_{ext}$$

Input and Output Capacitances

Input Capacitances for CMOS gates are the Gate capacitances:

C<sub>GB</sub>

C<sub>GS</sub>

C

Output Capacitances for CMOS gates are the drain capacitances:

| 12

$C_{DBP}$

$C_{GDN}$

**GBN**

$C_{GSN}$

out

, DBN

SBN

Cout = Cm2 + C

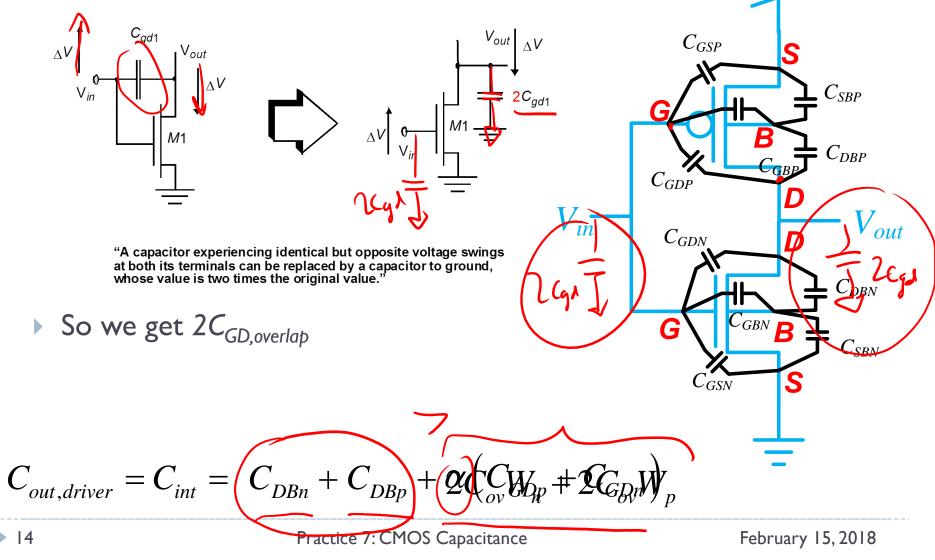

- Driver Capacitance

- We will start by looking at the Output Capacitance of the Driver:

- C<sub>DBn</sub> is between Vout and ground.

- Without losing too much accuracy, we will assume that C<sub>DBp</sub> is to ground.

- But we have another component of the output capacitance:  $V_{in}$

- The feedthrough capacitance from Vin to Vout  $(C_{GDp} \text{ and } C_{GDn}).$

- These are mainly overlap capacitances!

- But what is their size?

$$C_{out,driver} = C_{int} = C_{DBn} + C_{DBp} + \alpha \left( C_{GDp} + C_{GD} \right)$$

#### Driver Capacitance

• We need to consider the Miller Effect:

# Load Input Capacitance

- We look at all the capacitances connected to the gates of the load:

- ► C<sub>GSn</sub> and C<sub>GBn</sub> are between Vout and ground.

- Without losing much accuracy, we will assume  $C_{GSp}$  and  $C_{GBp}$  are to ground.

- Since we change from 0 to V<sub>DD</sub>/2, most of the time one transistor is cut-off, while the other is linear.

- So we can say that  $C_G = C_{ox}WL$  and not separate  $C_{GB}$ ,  $C_{GS}$  and  $C_{GD}$ .

$$C_{in,load} = \mathbb{C}_{GSn} \mathbb{W}_n \mathbb{L}_{nGBn} + \mathbb{C}_{GSp} \mathbb{W}_p + \mathbb{L}_{pGBp}$$

GBN

$C_{SBP}$

$C_{DBP}$

**V**<sub>out</sub>

$C_{DBN}$

$C_{SBN}$

$C_{GSP}$

$C_{GDP}$

$C_{GDN}$

U<sub>GSN</sub>

# Load Input Capacitance

- But what about Miller?

- Remember, this is a non-accurate **approximation**!  $C_{GSP}$

- There is very little Miller effect on the second stage because it hasn't started to switch.

- Considering that  $L=L_{eff}+2L_{ov}$ , we will usually just use  $C_{in}=C_{ox}WL$ .

$$C_{in,load} = C_{ox}W_nL_n + C_{ox}W_pL_p$$

GBN **B**

$C_{SBP}$

$C_{DBP}$

*V*<sub>out</sub>

$C_{DBN}$

$C_{SBN}$

$C_{GDP}$

G

$C_{GSN}$

$C_{GDN}$

$V_{in}$

#### **CMOS** Capacitances - Summary

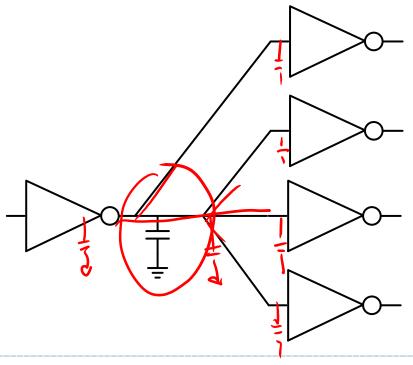

# Examples

Find the output capacitance of an inverter driving 4 identical inverters with:

$$\underbrace{C_{ov}}_{W_n} = 0.31 \text{ fF}/\mu\text{m}; C_{ox} = 6 \text{ fF}/\mu\text{m}^2; C_{DBp} = 1.5 \text{ fF}; C_{DBn} = 1.15 \text{ fF}; W_n/L_n = 0.375 \mu/0.25 \mu; W_p/L_p = 1.125 \mu/0.25 \mu; C_{wire} = 0.5 \text{ fF}; C_{wire} = 0.5 \text{ fF$$

• We'll just use the estimations we developed:

$$C_{out,driver} = C_{DBn} + C_{DBp} + 2C_{ov}W_n + 2C_{ov}W_p$$

= 1.5 fF + 1.15 fF + 2.0.31.0.375 fF + 2.0.31.125 fF = 3.58 fF

$$C_{\text{in,load}} = C_{ox}W_nL_n + C_{ox}W_pL_p$$

=  $6 \cdot 0.375 \cdot 0.25 + 6 \cdot 1.125 \cdot 0.25 \, fF = 2.25 \, fF$

$$C_{out} = C_{out,driver} + C_{wire} + 4 \cdot C_{in,load} = 3.58 + 0.5 + 9 = 13.08 \, fF$$

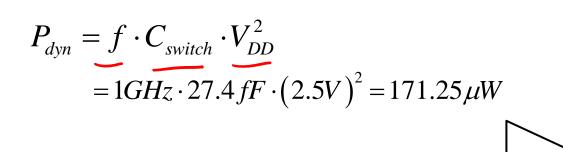

Now find the total power consumption of the circuit operating at a frequency of *IGHz* with a 2.5V supply.

$C_{switch} = C_{out} (stage1) + C_{out} (stage2) = C_{out} + 4 \cdot C_{out,driver}$  $= 13.08 \, fF + 4 \cdot 3.58 \, fF = 27.4 \, fF$

$P_{static} = 0$

308.

#### Exercise 2: Moed B 2010

שאלה 3 (10%)

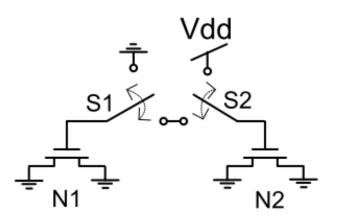

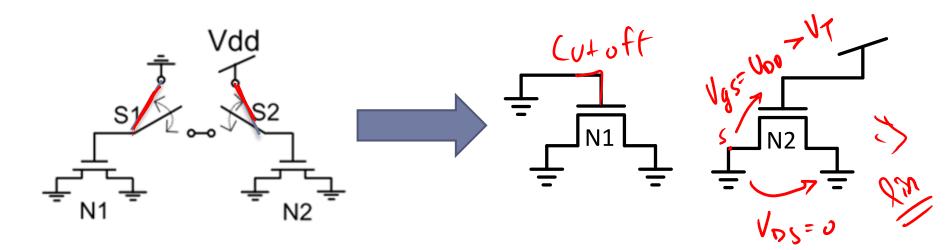

נתונים שני טרנזיסטורי NMOS בגודל מינימלי. המצעים שלהם מחוברים לאדמה. לכל טרנזיסטור מחובר מתג אידיאלי. במצב התחלתי המתג S1 מחבר את N1 לאדמה ומתג S2 מחבר את N2 למתח 1.8V.

. CGB , CGB , CGS א. (4) עבור כל אחד מהטרנזיסטורים יש לרשום בצורה פרמטרית את גודלם של קיבולי

#### Exercise 2: Moed B 2010

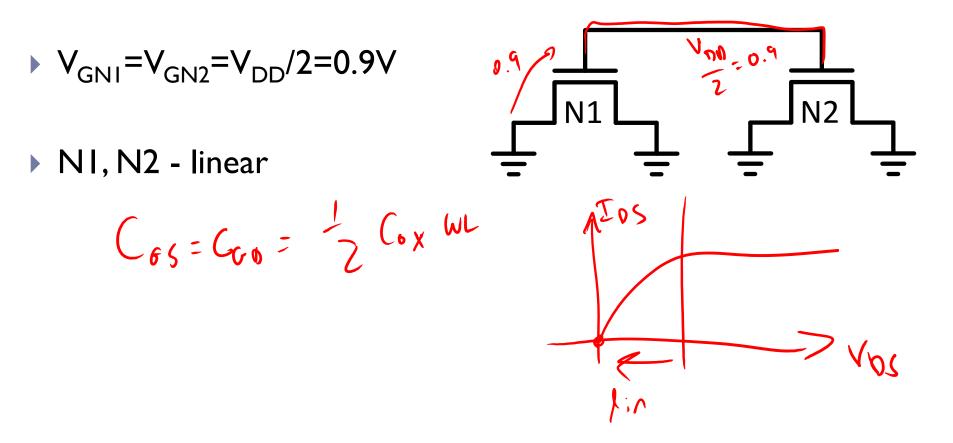

► NI – cut-off

$C_{CB} = C_{OX} W$ N2 - linear  $C_{45} = G_{0} = \frac{1}{2} C_{0} W L$

#### Exercise 2: Moed B 2010

ב. (6) כעת שני המתגים מחליפים מצב ומחברים בין את השערים של הטרנזיסטורים אחד לשני. מה יהיה הפוטנציאל בשער של כל אחד מהטרנזיסטורים מיד לאחר המיתוג? עבור כל אחד מהטרנזיסטורים יש לרשום בצורה פרמטרית את גודלם של קיבולי C<sub>GD</sub>, C<sub>GS</sub> ו-C<sub>GB</sub> לאחר המיתוג.