#### Practice 6:

# CMOS Digital Logic

Digital Electronic Circuits – Semester A 2012

#### The MOSFET as a Switch

# The MOSFET as a Switch

- We can look at the MOSFET as a Switch, passing the data between the diffusions when it's on, and blocking the data when it's off:

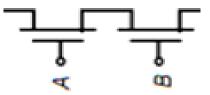

- An nMOS is on when it's gate is high:

• A pMOS is on when it's gate is low:

# **ANDing and ORing**

- It is important to recognize the functionality of a serial and parallel connection of switches:

- Connecting switches serially, creates an AND function:

• Connecting switches in parallel, creates an OR function.

# Strong and Weak Levels

- MOSFETs are imperfect switches for various reasons. One of them is the fact that each type of device is only good at passing one kind of signal:

- nMOS is good at passing a '0':

But bad at passing a 'l':

• We like to say that the nMOS passes a "weak '1""

# **Pull Up and Pull Down Networks**

- Since the nMOS is good at passing a '0', and the pMOS is good at passing a '1', we will:

- Use nMOS devices to pull down the output.

- ▶ Use pMOS devices to *pull up* the output.

#### • Therefore:

- Non-inverted inputs to the nMOS create an inverted output.

- Inverted inputs to the pMOS create a non-inverted output.

- This is what we got from the DeMorgan identities!

# **Creating a NAND Gate**

- We now can use these principles to create a NAND gate:

- The pull-down network of the NAND gate provides a '0' when both inputs are high.

- The pull-up network provides a 'l' for all other cases.

- These two conditions are complementary so connecting them to the same output doesn't create a contention.

- Instead, it creates a complete function.

| Α | В | PDN | PUN | NAND |

|---|---|-----|-----|------|

| 0 | 0 | Z   | I   | I    |

| 0 | I | Z   | I   | I    |

| I | 0 | Z   | I   | I    |

| I |   | 0   | Z   | 0    |

# Example: Constructing a CMOS Gate

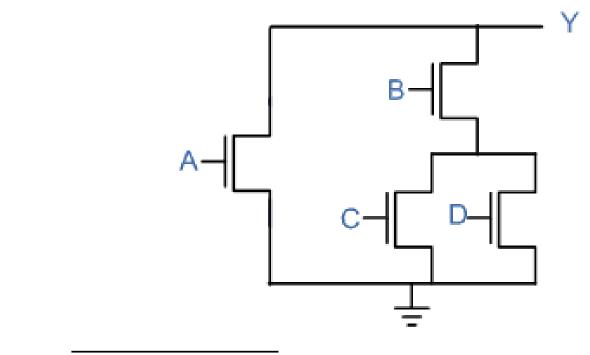

- Given a Pull Down Network:

- A) Find the logic function of the given circuit:

$$f(A,B,C,D) = A + B(C+D)$$

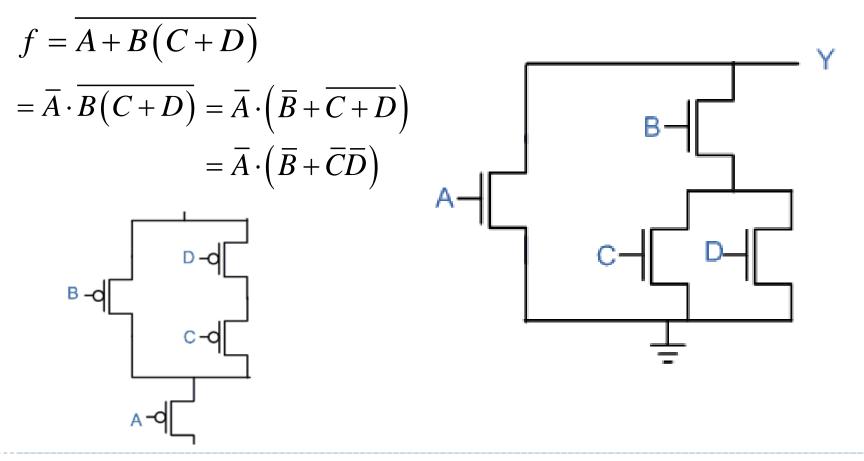

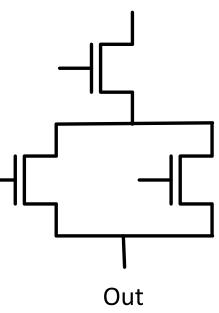

# Example: Constructing a CMOS Gate

- Given a Pull Down Network:

- B) Construct the PUN of the function

# Transistor Sizing

# **On Resistance of a MOS Switch**

According to our unified current model, the current of a transistor is proportional to the transconductance (K):

$$I_{DS} = K \left( V_{GT} V_{DS,eff} - 0.5 V_{DS,eff}^2 \right) \left( 1 + \lambda V_{DS} \right)$$

$$K = \mu C_{ox} \frac{W}{L}$$

- Therefore the current increases with W and decreases with L.

- This is equivalent to saying resistance increases with L and decreases with W.

#### February 15, 2018

Practice 6: CMOS Digital Logic

• Connecting two transistors with the same length in parallel is similar to increasing their widths.  $\frac{W_1}{L} \| \frac{W_2}{L} \Leftrightarrow \frac{(W_1 + W_2)}{L}$

• Connecting two transistors with the same width in series is equivalent to increasing their lengths:  $\frac{W}{L_1} + \frac{W}{L_2} \Leftrightarrow \frac{W}{(L_1 + L_2)}$

Transistor Connection Equivalence

**Transistor Connection Equivalence**

In general, since:

$$R_{eq} \propto \frac{1}{K} \propto \frac{L}{W}$$

When connecting transistors in series:

$$R_{series} = R_{eq1} + R_{eq2} + \dots \propto \frac{1}{k_1} + \frac{1}{k_2} + \dots$$

When connecting transistors in parallel:

$$R_{parallel} = \frac{1}{R_{eq1}} + \frac{1}{R_{eq2}} + \dots \propto k_1 + k_2 + \dots$$

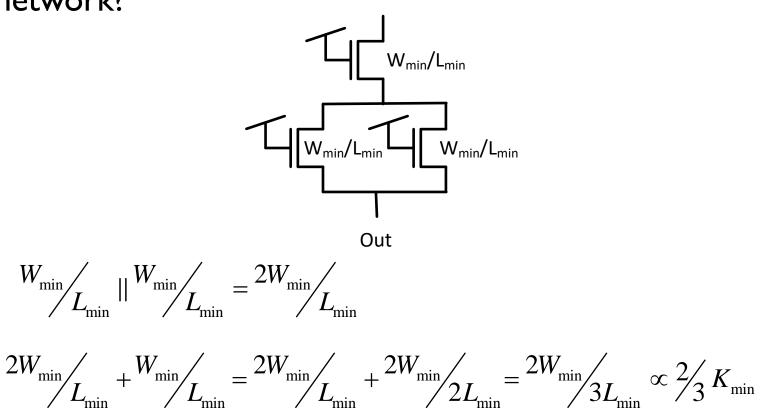

# Example: Equivalent Transconductance

What is the equivalent transconductance of the following network?

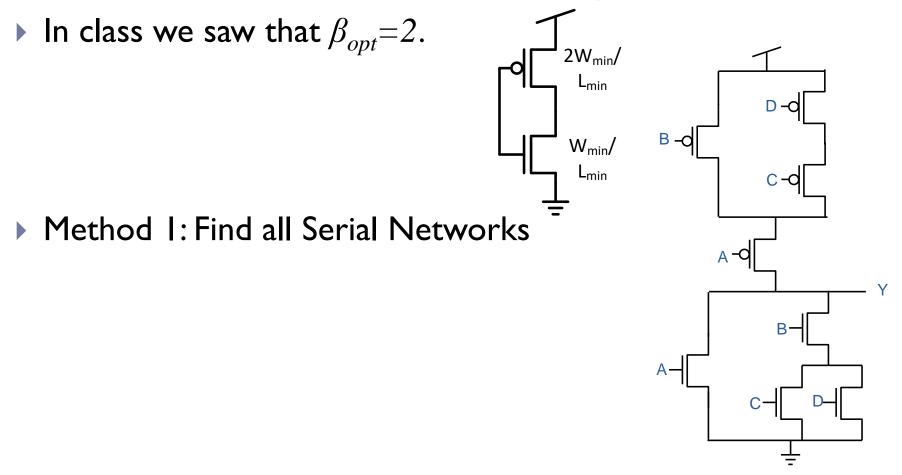

#### Example: Worst Case Path

- However, we can only set the size according to the Worst Case Path so we will look for serially connected networks:

- Then we will size the devices to be equivalent to one minimally sized nMOS:

In

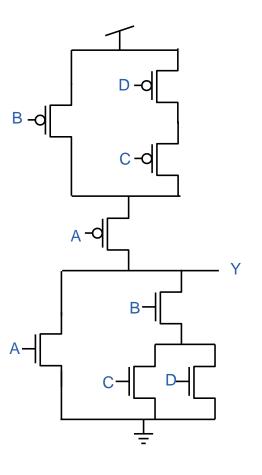

# Example: Sizing a CMOS Gate

Now we can go back to sizing our complex CMOS Gate.

# Example: Sizing a CMOS Gate

- Method 2: Find all Serial Networks

- For the PUN, we find the worst case path.

• Then to size the remaining devices we will use the equation:

$$\frac{1}{W_{peq}/L_{peq}} = \frac{1}{W_{pA}/L_{pA}} + \frac{1}{W_{pA}/L_{pA}}$$

$$\frac{1}{2W_{\min}} = \frac{1}{W_{pA}} + \frac{1}{W_{pB}} = \frac{1}{6W_{\min}} + \frac{1}{W_{pB}}$$

$$W_{pB} = 3W_{\min}$$

$W_{peq} = 2W_{\min}$

$L_i = L_{\min}$

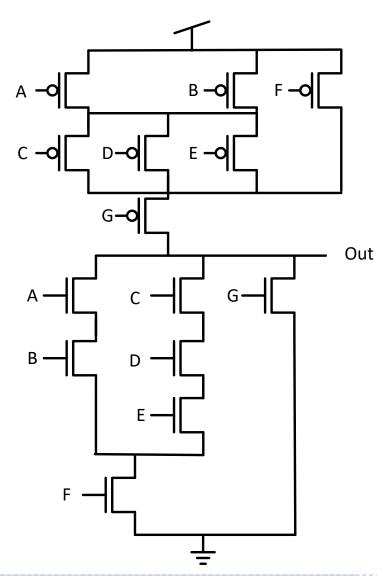

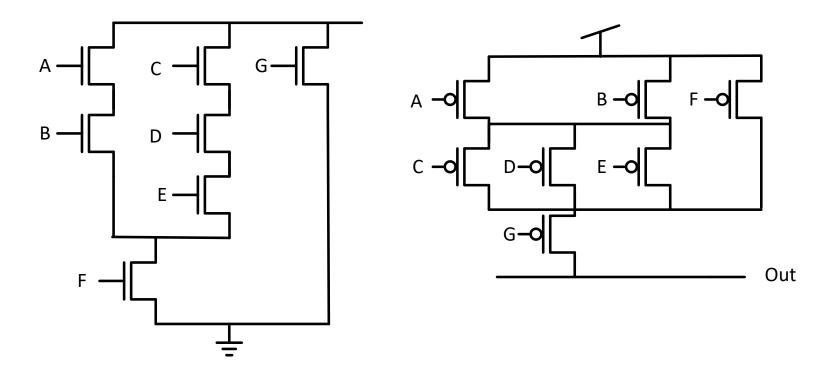

- Given the equation:  $f = ((\overline{A} + \overline{B})(\overline{C} + \overline{D} + \overline{E}) + \overline{F})\overline{G}$

- A) Build a CMOS gate that realizes the equation

- **B**) Size the gate with  $(W/L)_n = 2 (W/L)_p = 6$

- C) What are the best and worst case patterns for PUN and PDN resistance?

• A) First we'll find the appropriate PDN for the given function.

$$f = \overline{\left(\left(\overline{A} + \overline{B}\right)\left(\overline{C} + \overline{D} + \overline{E}\right) + \overline{F}\right)\overline{G}} = \overline{\left(\overline{A} + \overline{B}\right)\left(\overline{C} + \overline{D} + \overline{E}\right) + \overline{F}} + \overline{G} = \overline{\left(\overline{A} + \overline{B}\right)\left(\overline{C} + \overline{D} + \overline{E}\right)} \cdot F + \overline{G} = \overline{\left(\overline{A} + \overline{B} + \overline{C} + \overline{D} + \overline{E}\right)} \cdot F + \overline{G} = \overline{\left((A \cdot B) + (C \cdot D \cdot E)\right)} \cdot F + \overline{G}}$$

Now we can draw our logic gate.

$$f = \underbrace{\left(\left(\overline{A} + \overline{B}\right)\left(\overline{C} + \overline{D} + \overline{E}\right) + \overline{F}\right)\overline{G}}_{PUN} = \underbrace{\left(\left(A \cdot B\right) + \left(C \cdot D \cdot E\right)\right) \cdot F + G}_{PDN}$$

- **B)** Next we will size the PDN according to  $(W/L)_n = 2$

- Finally, we will size the PUN according to  $(W/L)_p = 6$

- C) Best case patterns:

- High to Low Transition

- Low to High Transition

- Worst Case Patterns:

- High to Low Transition

- Low to High Transition