# Digital Integrated Circuits (83-313)

# Lecture 3: MOSFET Modeling

27 April 2020

Emerging Nanoscaled Integrated Circuits and Systems Labs

Disclaimer: This course was prepared, in its entirety, by Adam Teman. Many materials were copied from sources freely available on the internet. When possible, these sources have been cited; however, some references may have been cited incorrectly or overlooked. If you feel that a picture, graph, or code example has been copied from you and either needs to be cited or removed, please feel free to email <u>adam.teman@biu.ac.il</u> and I will address this as soon as possible.

#### Lecture Content

# TCAD vs. Compact Models

- Technology CAD (TCAD) is a simulation environment for accurately simulating device behavior:

- Provide a process "recipe" and device layout

- Produce IV or CV curves through device simulator

- Used to predict device and process physics

- Takes 1hr-1day per IV curve and 100s MB RAM per transistor

- Compact models (a.k.a. SPICE models or ECAD) are simple models used for circuit simulation

- Provide a set of equations that SPICE uses to calculate IV or CV curves

- Should take <100us per IV curve and a few KB per transistor

- Usually extracted empirically from measurements

TCAD is too **slow** and **memory hungry** to be used for circuit simulation!

SPICE uses *compact models* for calculating device behavior

© Adam Teman, 2020

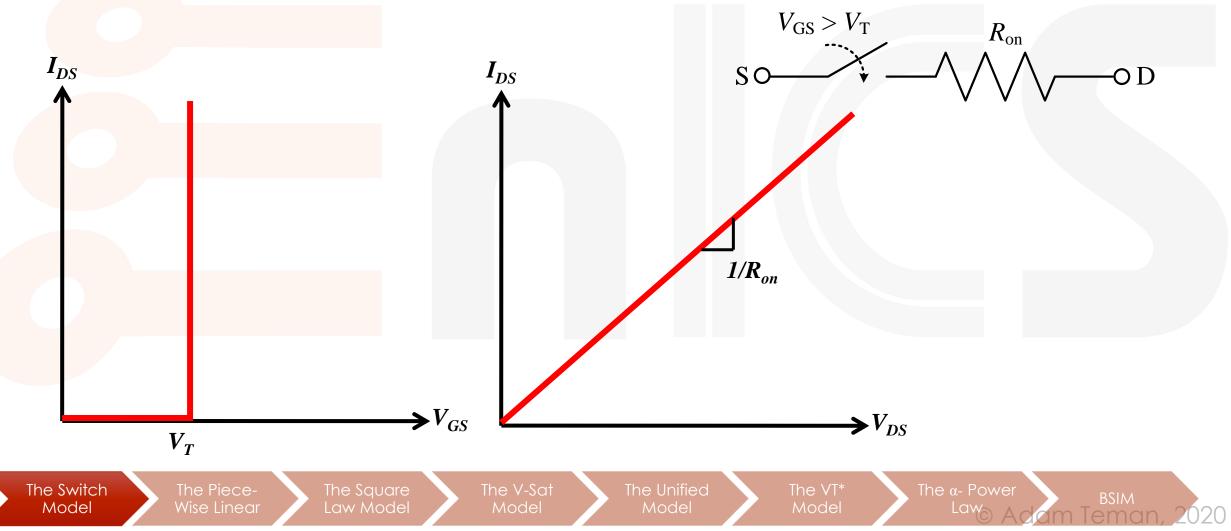

# Switch Model

6

• The most simple MOSFET model is the Switch Model.

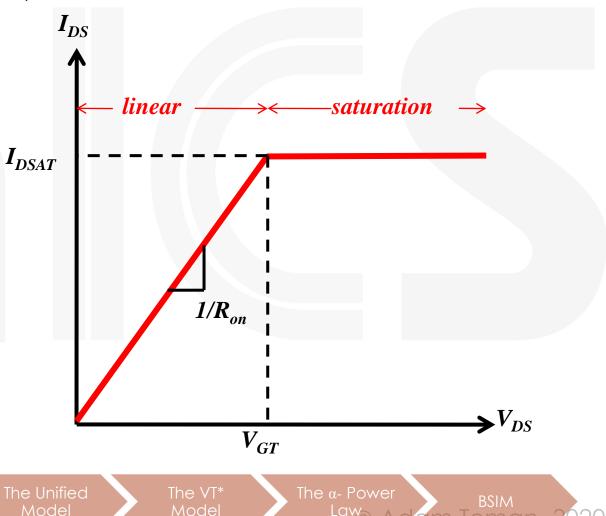

# **The Piece-Wise Linear Model**

• As we know, when the channel pinches off, the current saturates.

The Square

Law Model

The V-Sat

Model

This can be depicted with the simple

Piece-Wise Linear Switch Model

The Piece-

Wise Linear

The Switch

Model

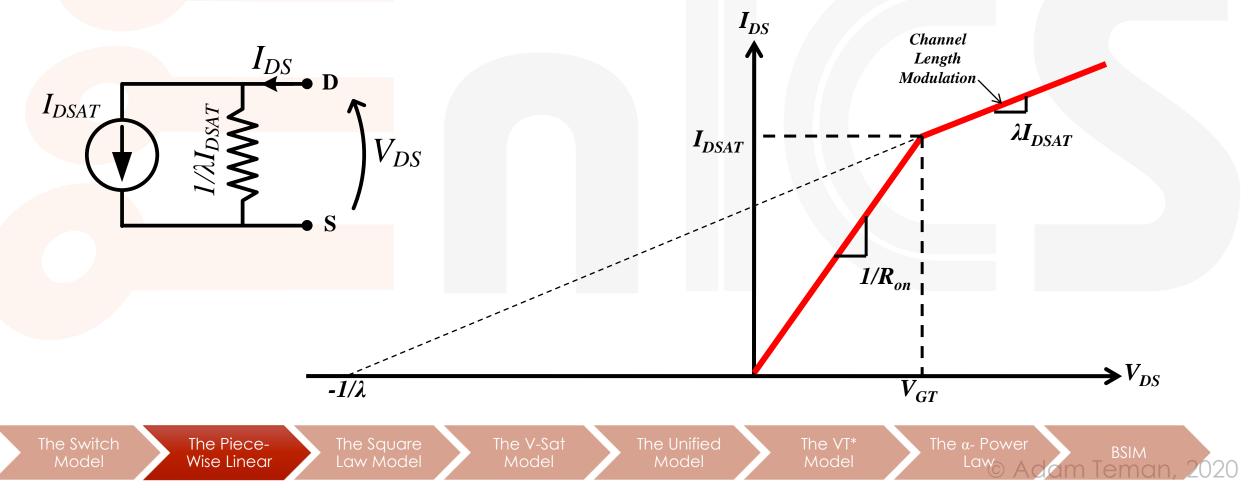

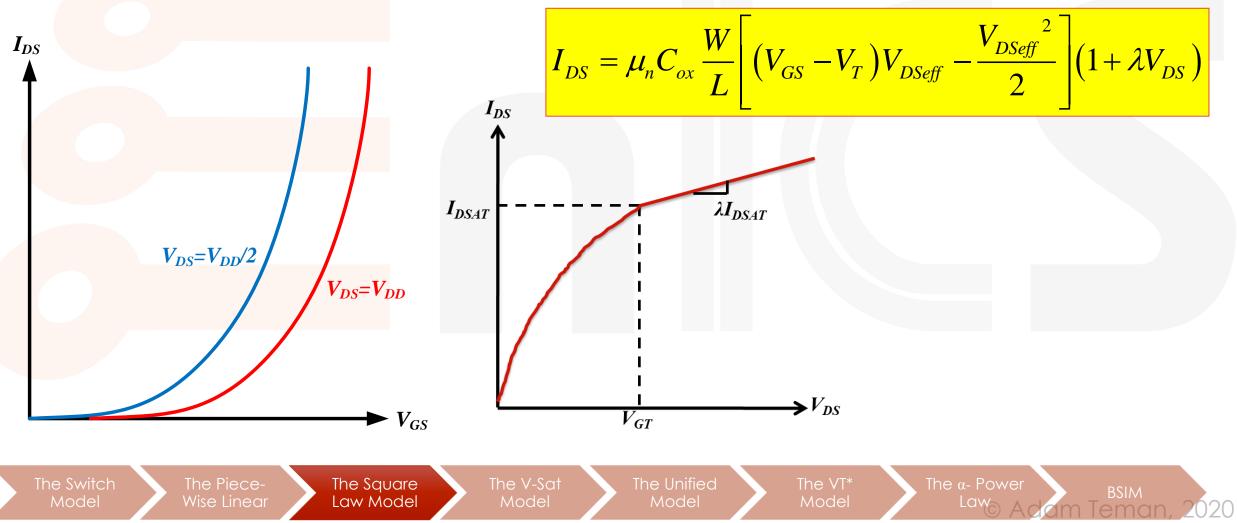

# **Adding Channel Length Modulation**

• Channel Length Modulation modeled as a finite output resistance, causes a saturation current dependence on  $V_{\rm DS}$ .

8

# Square Law (Shockley) Model

- To get a more accurate model, we already are familiar with the Shockley or Square Law Model.

- Current is just charge times velocity, so at any point, *x*, along the channel:

$I_D(x) = -\nu(x)Q(x)Wdx$

We found that charge can be approximated as:

The Square

Law Model

$$Q(x) = -C_{ox} \left[ V_{GS} - V_{CS}(x) - V_T \right]$$

And the velocity is the mobility times the electrical field:

$$v(x) = -\mu E(x) = \mu_n \frac{dV}{dx}$$

The Unified

Model

Model

The V-Sat

Model

The Switch

Model

The Piece-

Wise Linear

# Square Law (Shockley) Model

• So we get:

$$I_D dx = \mu_n C_{ox} W \left( V_{GS} - V - V_T \right) dV$$

And integrating from source to drain, we get

$$I_{DS} = \int_{0}^{L} I_{D} dx = \int_{0}^{V_{DS}} \mu_{n} C_{ox} W \left( V_{GS} - V - V_{T} \right) dV = \mu_{n} C_{ox} \frac{W}{L} V_{DS} \left( V_{GS} - V_{T} - \frac{1}{2} V_{DS} \right)$$

• At pinch-off ( $V_{DS} = V_{GS} - V_{T}$ ), the voltage over the channel is constant, so we get:

The Unified

Model

Model

The α- Power

$$I_{DSAT} = \mu_n C_{ox} \frac{W}{2L} (V_{GS} - V_T)^2$$

The V-Sat

Model

• This is where the "Square-Law" name comes from.

The Square

Law Model

The Switch

Model

The Piece-

Wise Linear

# Square Law (Shockley) Model

• Replacing  $V_{\text{DS}}$  with  $V_{\text{DSeff}} = \min(V_{\text{GS}} - V_{\text{T}}, V_{\text{DS}})$  we get:

11

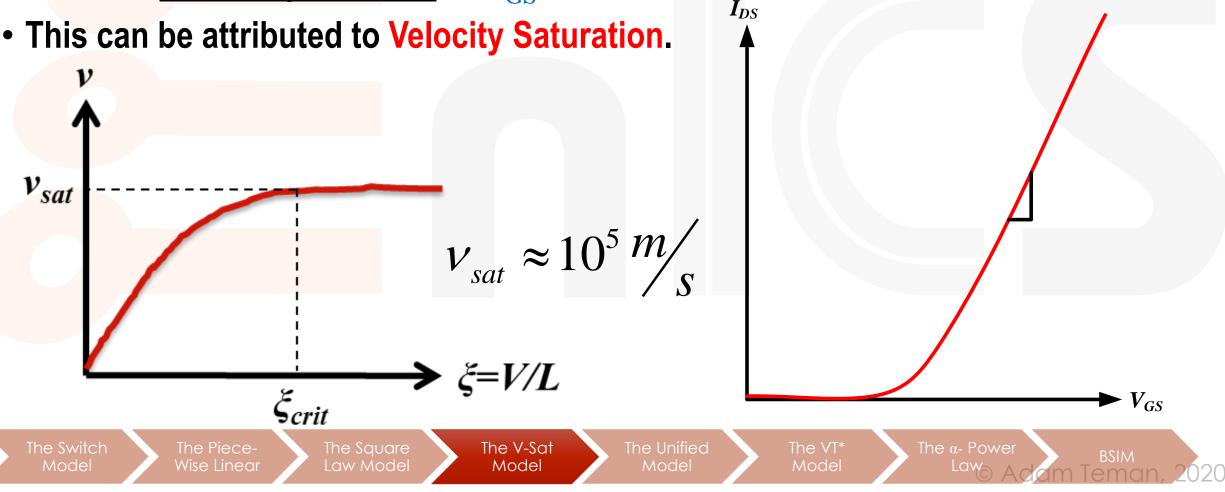

# **The Velocity Saturation Model**

- However, when looking at a short channel device, we see a linear dependence on  $V_{GS}$ .

- This can be attributed to Velocity Saturation.

12

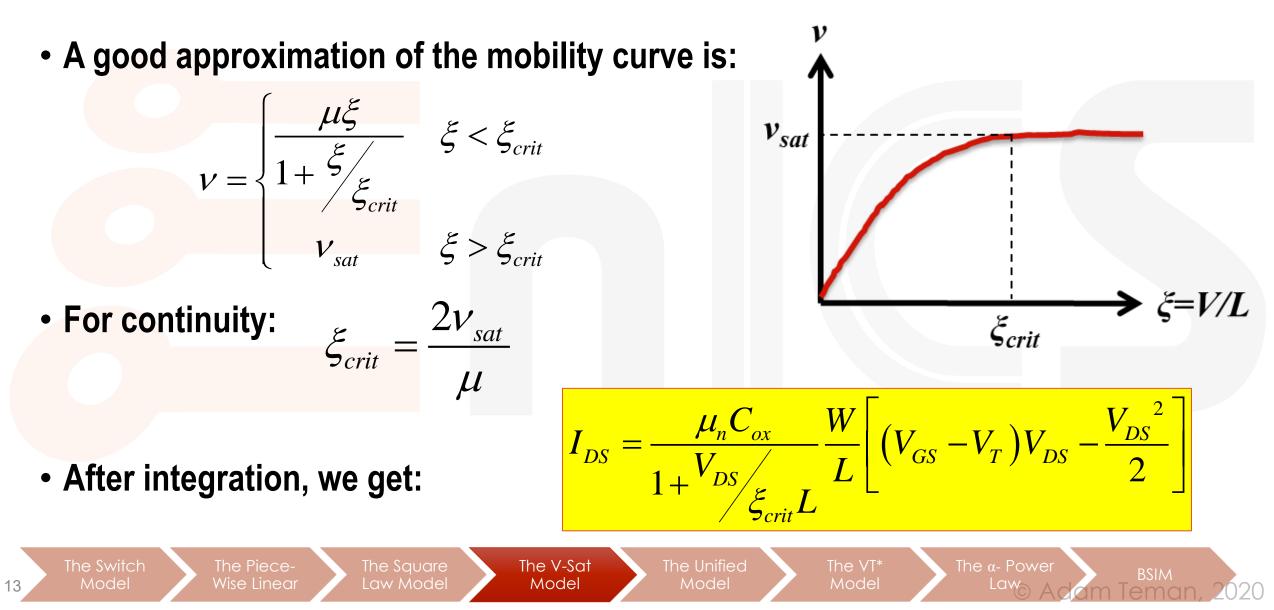

# **The Velocity Saturation Model**

# The Velocity Saturation Model

- This is hard to use, but we can reach an important conclusion.

- We found that:  $I_{DS} = \frac{\mu_n C_{ox}}{1 + \frac{V_{DS}}{\xi_{crit}L}} \frac{W}{L} \left[ \left( V_{GS} - V_T \right) V_{DS} - \frac{V_{DS}^2}{2} \right]$

The V-Sat

Model

The Unified

Model

And we know that for a velocity saturated device:

The Square

Law Model

$$I_{DS} = WC_{ox} \left( V_{GS} - V_{DSAT} - V_T \right) v_{sat}$$

• Equating, we get:

$$V_{DSAT} = \frac{\left(V_{GS} - V_T\right)\xi_{crit}L}{\left(V_{GS} - V_T\right) + \xi_{crit}L}$$

The Piece-

Wise Linear

$$V_{DSAT} \left( \xi_{crit} L >> V_{GT} \right) = V_{GS} - V_T \Rightarrow pinch off$$

$$V_{DSAT} \left( \xi_{crit} L << V_{GT} \right) = \xi_{crit} L \Rightarrow vel sat$$

Model

The α- Power

The Switch

Model

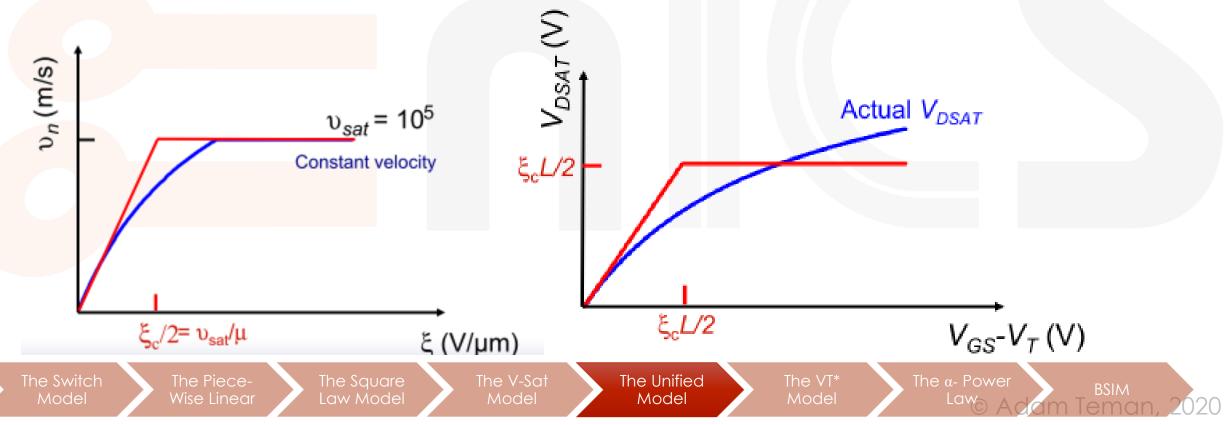

# **The Unified Model for Hand Analysis**

- A few simple estimations will make the V-Sat model more user-friendly:

- The mobility is piecewise linear, saturating at  $\zeta > \zeta_{crit}/2$

15

•  $V_{\text{DSAT}}$  is piecewise linear, saturating at  $V_{\text{DSAT}} = \xi_{\text{crit}} L/2$ , when  $V_{\text{GT}} > \xi_{\text{crit}} L/2$

# **The Unified Model for Hand Analysis**

• This brings us to the Unified Model:

$$I_{DS} = \mu_n C_{ox} \frac{W}{L} \left[ (V_{GS} - V_T) V_{DSeff} - \frac{V_{DSeff}^2}{2} \right] (1 + \lambda V_{DS})$$

$$V_{DSeff} = \min \left( V_{GS} - V_T, V_{DS}, V_{DSAT} \right)$$

$$V_{DSAT} = \frac{\xi_{crit} L}{2} \quad \xi_{crit} = \frac{2v_{sat}}{\mu}$$

The Switch Model

16

The Piece-Wise Linear Law Model The V-Sat Model The Unified Model The VT\* Model The α- Power Law

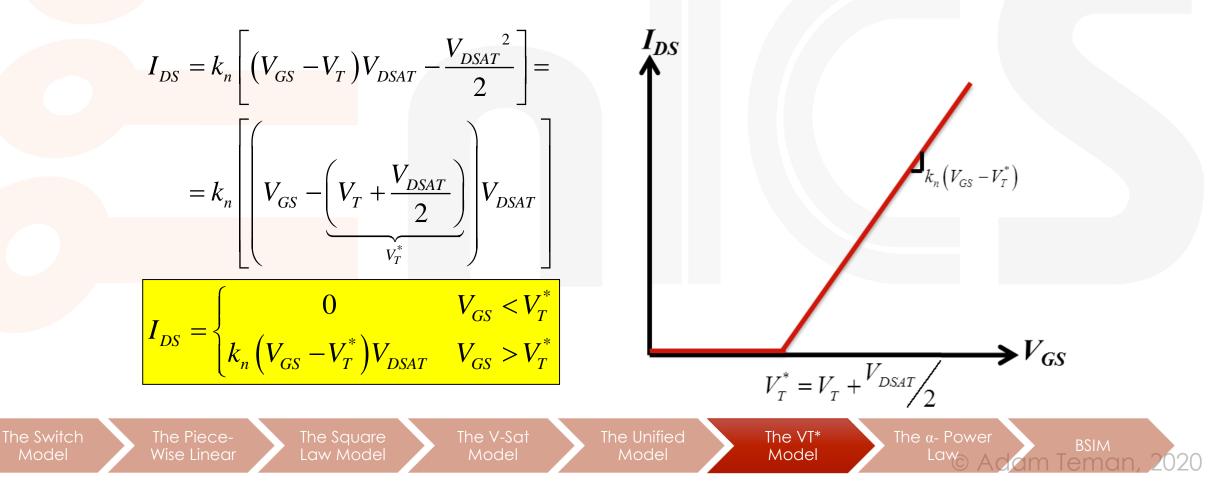

#### **VT\* Model**

18

- Sometimes we want to use a really simple model.

- We can assume that if the transistor is on, it's velocity saturated.

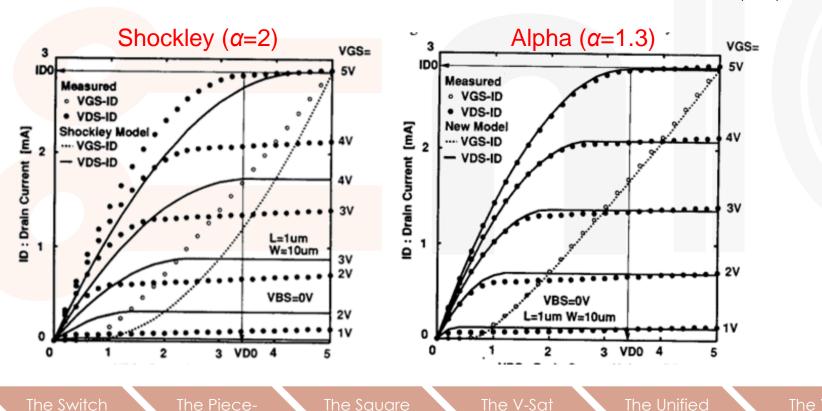

# The Alpha Power Law Model

• Sakurai found that by <u>changing the exponent</u> of the square law, a better fit can be found with simple calculations. W

Model

Law Model

Wise Linear

$$D_{DSAT}(\alpha) = \mu_n C_{ox} \frac{W}{2L} (V_{GS} - V_T)^{\alpha}$$

The  $\alpha$ - Power

Law

Model

Model

19

Model

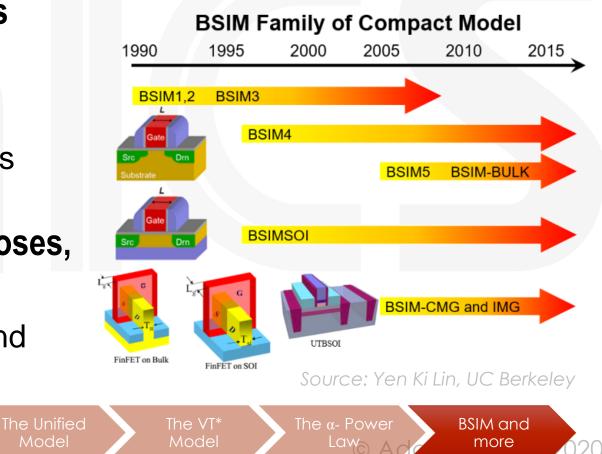

# **BSIM and Newer Models**

- **BSIM** (Berkeley Short-channel IGFET Model) is the primary compact model family used for SPICE simulation for the last three decades.

- These model use hundreds of parameters to achieve a good fit.

- BSIM4 is the main model for bulk CMOS

- Takes into account most physical effects as well as many fitting parameters.

- The Compact Model Coalition (CMC) chooses, maintains and promotes new models

- Additional models include EKV, PSP, and models for non-MOS devices.

The Square

Law Model

The V-Sat

Model

Model

The Piece-

Wise Linear

The Switch

Model

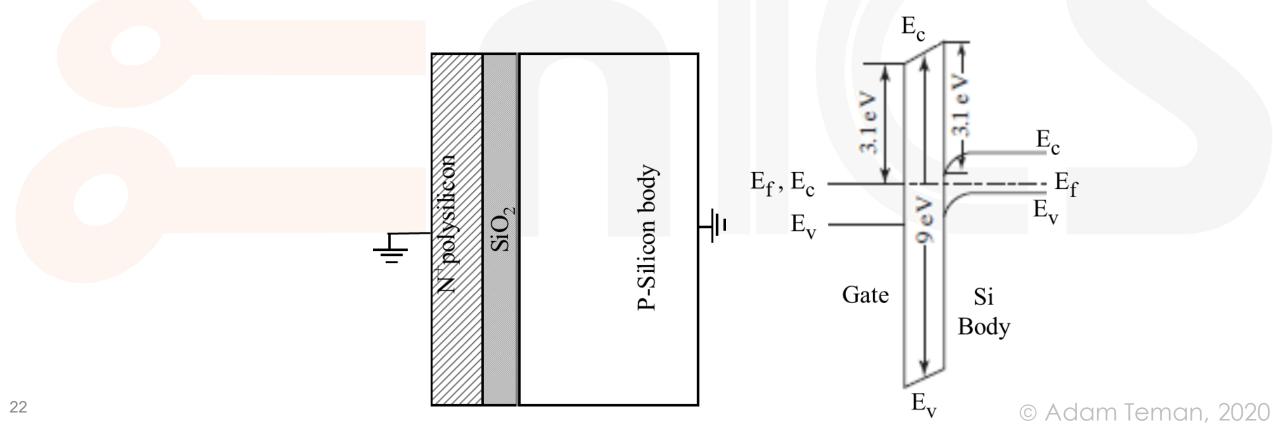

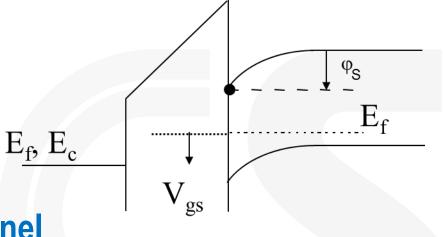

# **Energy Band Diagrams**

- To understand the threshold voltage and other secondary effects of the MOS device, we often use energy band diagrams.

- The first approach is looking in from the gate:

# **Energy Band Diagrams**

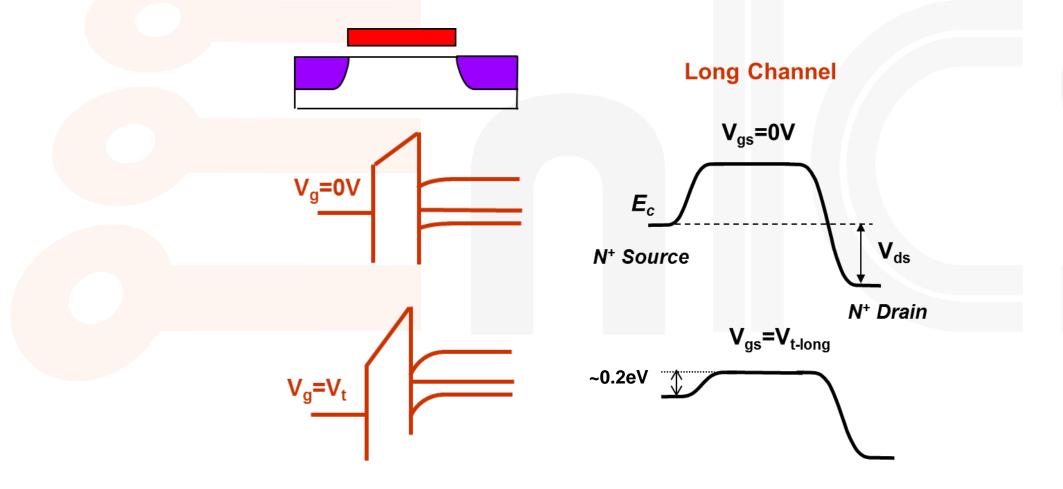

• The second approach is looking from the source to the drain.

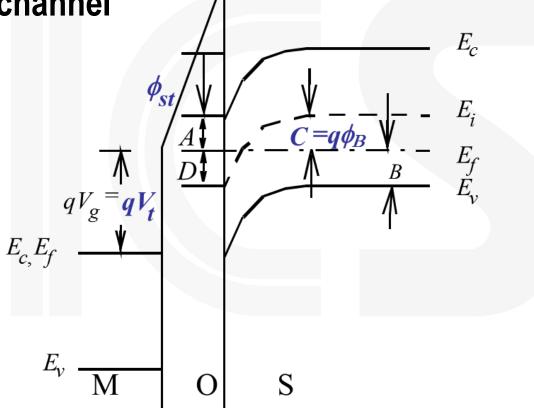

# **Threshold Voltage - Basic Theory**

• The basic definition of threshold voltage is the gate voltage ( $V_{\rm G}$ ) required to invert the channel

$$V_{T0} = \Phi_{MS} - 2\Phi_F - \frac{Q_{OX}}{C_{ox}} - \frac{Q_{dep}}{C_{ox}} - \frac{Q_I}{C_{ox}}$$

$$Q_{dep} = \sqrt{2qN_A\varepsilon_{si}} \left| -2\Phi_F \right|$$

$$\Phi_F = -\phi_T \ln \frac{N_A}{n_i} \qquad \phi_T \equiv \frac{kT}{q}$$

Classic Body

Effect

RSCE

Measuring VT

24

DIBL

25

This can be modeled by the additional charge that needs to be depleted.

$$\mathcal{Q}_{dep} = \sqrt{2qN_A\varepsilon_{si}\left(\left|-2\Phi_F + V_{SB}\right|\right)}$$

$$\mathcal{V}_T = \mathcal{V}_{T0} + \gamma\left(\sqrt{\left|-2\Phi_F + V_{SB}\right|} - \sqrt{\left|-2\Phi_F\right|}\right)}$$

$$\mathcal{V}_{T0} \equiv \Phi_{MS} - 2\Phi_F - \frac{Q_{ox}}{C_{ox}} - \frac{Q_{dep0}}{C_{ox}}, \quad \gamma = \frac{\sqrt{2q\varepsilon_{si}N_A}}{C_{ox}}$$

and the set of the

The Body Effect

# Boo

- The appearance of a voltage difference between the source and body  $(V_{SB})$  is known as "The Body Effect"

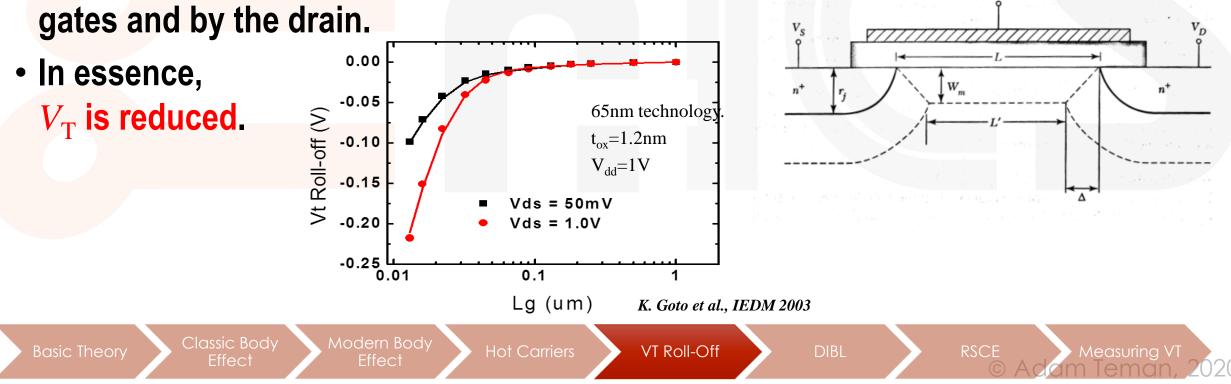

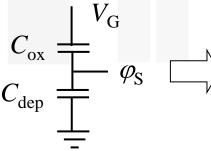

# **Modern Body Effect**

26

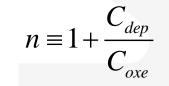

A different approach is to look at the capacitive voltage divider between the gate and body ( $C_{GB}$ )  $Q_{inv} = -C_{oxe} \left( V_{GS} - V_{CS} - V_{T0} \right) + C_{dep} \left( V_{SB} + V_{CS} \right)$  $= -C_{oxe} \left( V_{GS} - nV_{CS} - V_{T0} \right)$  $V_{\rm G}$ Gate  $n \triangleq 1 + \frac{C_{dep}}{C_{oxe}} = 1 + \frac{3T_{oxe}}{W_{d \max}}$  $C_{oxe} =$ Toxe  $C_{\rm oxe}$  $\Theta \Theta \Theta \Theta \Theta \Theta \Theta \Theta \Theta$  $V_s$ V<sub>S</sub> • S Ν Ν W<sub>dmax</sub> C<sub>dep</sub>  $C_{\mathrm{dep}}$ P-Body  $C_{dep}$  =  $V_h$ Classic Body Modern Body VT Roll-Off DIBL RSCE Measuring VT **Basic Theory** Effect Effect

# Modern Body Effect

• This can be shown to redefine  $V_{\rm T}$  as:

$$V_{\rm T}(V_{\rm SB}) = V_{\rm T0} + \frac{C_{\rm dep}}{C_{\rm oxe}} V_{\rm SB}$$

• In modern technologies,  $C_{dep}/C_{oxe}$  is a constant, so  $V_{T}$  is *linearly dependent* on  $V_{SB}$ !

27

Hot Carriers

VT Roll-Off

DIBL

Measuring VT

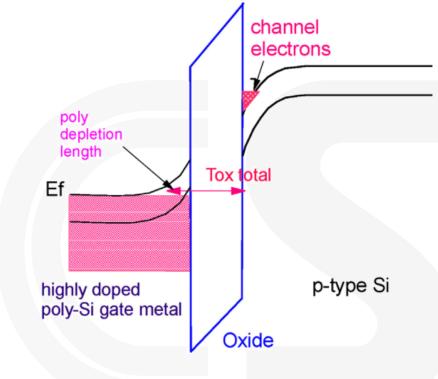

# **Poly Depletion and Channel Depth**

The threshold voltage is affected by two additional factors that we have disregarded until now:

- Polysilicon Depletion

- Since polysilicon is, itself, a semiconductor, the depletion layer into the poly effectively increases the oxide thickness.

- Channel Depth

- Since the channel is not a 2-dimensional line along the surface, the oxide thickness is essentially increased.

Effect

Measuring VT

RSCE

28

VT Roll-Off

DIBL

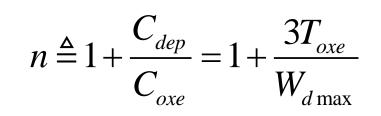

# **Hot Carrier Effects**

29

• Electrons can get so fast that they can tunnel into the gate oxide and increase the threshold voltage.  $V_{T0} = \Phi_{MS} - 2\Phi_{F} - \frac{Q_{OX}}{C} - \frac{Q_{dep}}{C} - \frac{Q_{I}}{C}$

• This is a reliability issue as it happens over time.

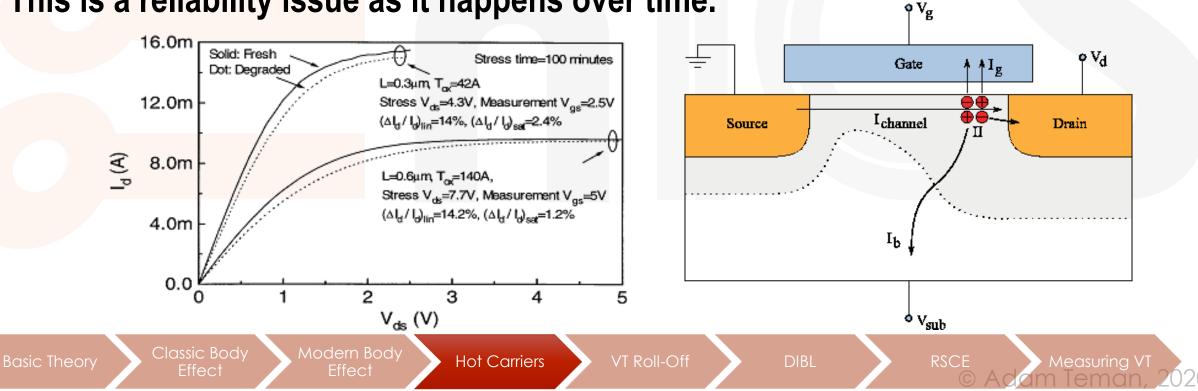

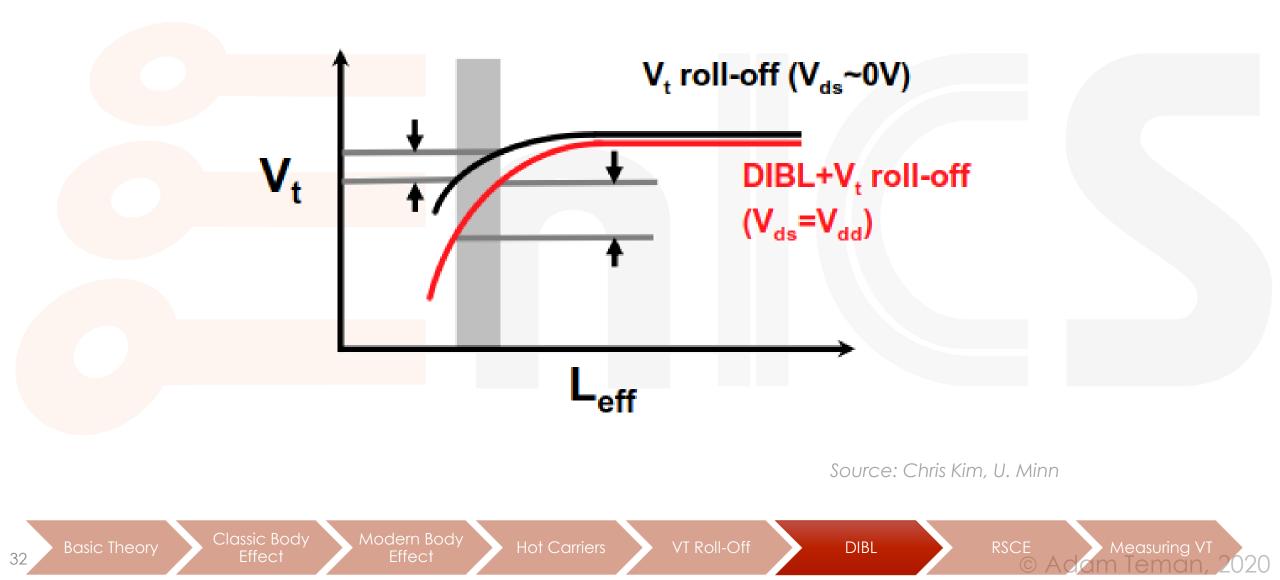

# V<sub>T</sub> Roll Off (Short Channel Effect)

- As channel length is reduced, effective channel length is reduced by depletion regions.

- A trapezoid is created under the gate, dividing the channel into the region controlled by the gates and by the drain.

30

source/channel

short channel

barrier

long channel

$V_{ds}$

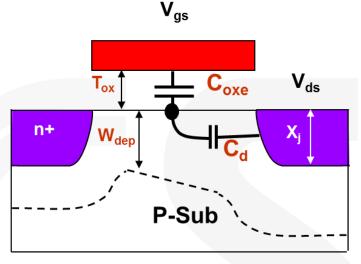

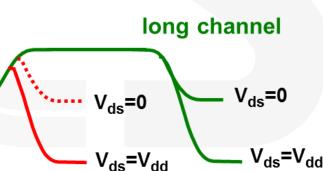

# **DIBL (Drain Induced Barrier Lowering)**

In short channels, the barrier of the channel is essentially lowered, as the drain causes the energy band to drop closer to the source.

$V_{DS}$

Modern Body

Effect

• This is exponentially dependent on  $V_{\rm DS}$ .

Measurina V1

short channel

oxe

DIBL

RSCE

31

Low V<sub>DS</sub> threshold

Classic Body

Effect

$V_{\tau}$

$V_{\rm T} = V_{\rm T,long} - \left(V_{\rm DS} + 0.4\right) \cdot \frac{C_{\rm d}}{C}$

# Roll Off / DIBL combined

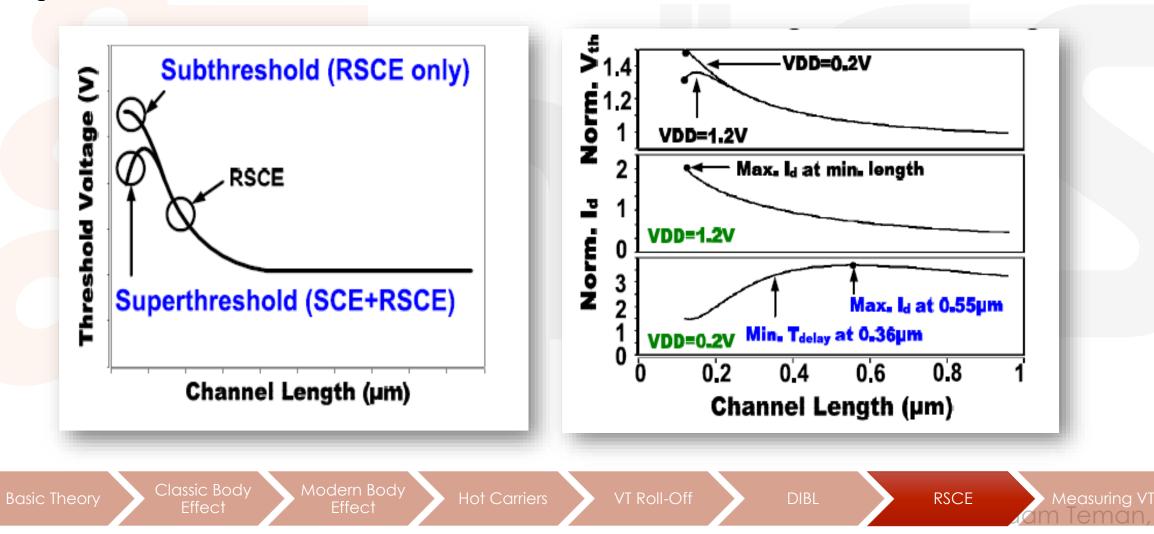

# **Reverse Short Channel Effect (RSCE)**

•  $V_{\rm T}$  actually *increases* at channel lengths a bit higher than minimum...

33

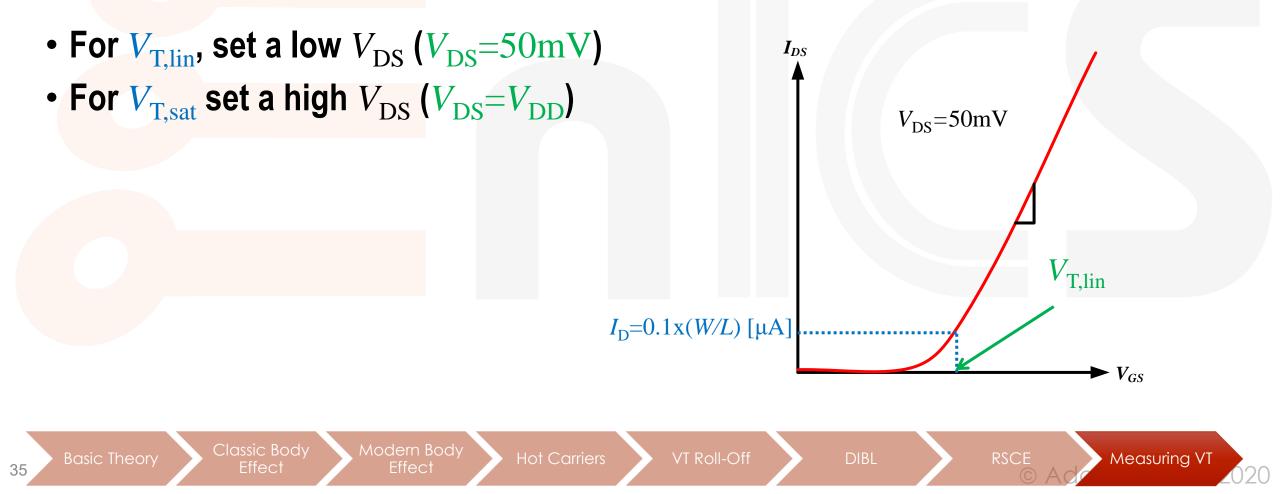

#### How to Measure VT

- There are various ways to measure  $V_{\rm T}$

- One classic way takes a small  $V_{\rm DS}$  and sweeps  $V_{\rm GS}$ .

$$I_d = k \left[ (V_{\rm GS} - V_{\rm T}) V_{\rm DS} - 0.5 V_{\rm DS}^2 \right] \propto V_{\rm GS} - V_{\rm T} \qquad I_{\rm DS}$$

• So we can find the  $V_{GS}$  at which the linear part crosses  $I_{ds}=0$ .

Modern Body

$$V_{DS}=50 \text{mV}$$

$V_{T,gm}$

$V_{T,gm}$

$V_{GS}$

Hot Carrier

VT Roll-Off

DIB

# How to Measure VT

• One of the more common ways is to find the  $V_{GS}$  at which  $I_{DS} = 100 \text{ nA x } W/L$ .

### Note about Simulation

• The first step of all Spice (Spectre) simulations is a DC Operating Point calculation.

# Simulation tip: OP and MP in Spectre

- So we saw that the threshold voltage is dependent on the operating point.

- How do you know what the the  $V_{\rm T}$  of a transistor is in a given simulation?

- To find  $V_{\rm T0}$ , use the "MP" option.

• To find  $V_{\text{T,lin}}$ ,  $V_{\text{T,sat}}$ ,  $V_{\text{T,gm}}$ , use the "OP" option.

• How would you go about plotting roll-off (SCE) and RSCE?

#### **The Computer Hall of Fame**

• We generally consider the ENIAC to be the first computer, but the official first fully electronic computer was the

Atansoff-Berry Computer

Conceived in 1937, operational in 1942

- Built at Iowa State University by Prof. John Atansoff and his student Clifford Berry.

- Not programmable nor Turing-complete, but included binary arithmetic and electronic switching elements.

- A patent dispute over the first electronic computer was settled in 1973, when the patent of the ENIAC was invalidated.

ource: wikipedia

# Simulating Variation

Process Corners and Monte Carlo Simulation

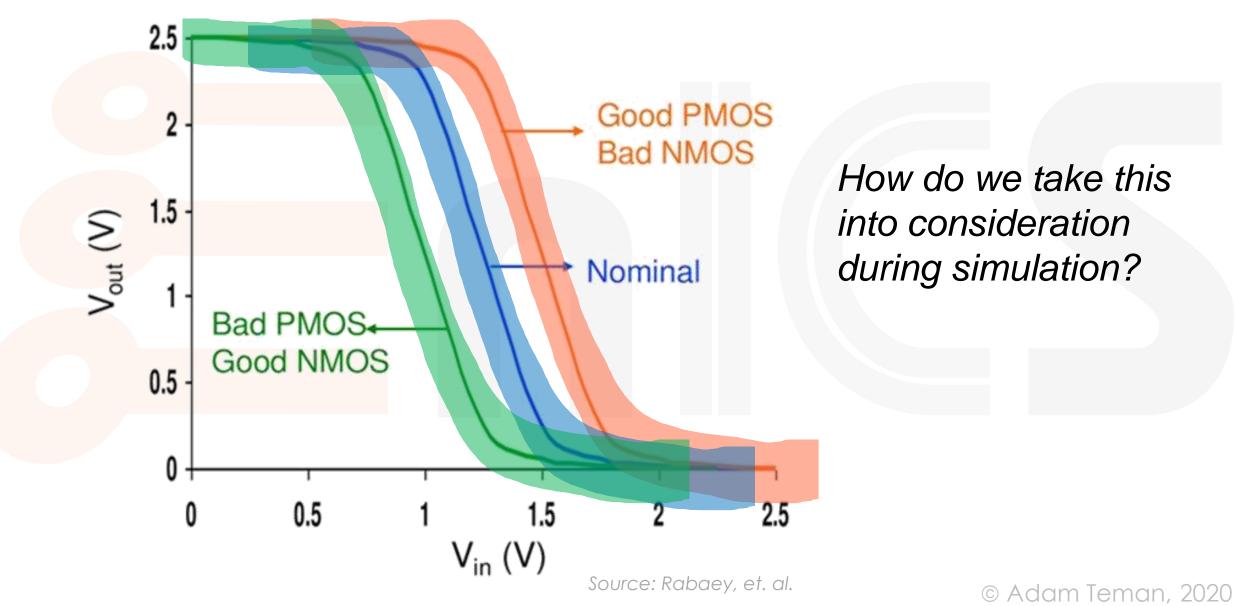

#### **Reminder: Impact of Process Variations**

#### **Remove the Rust: Probability Basics**

#### • Properties of Random Variables

• The probability distribution function (PDF) *f*(*x*) specifies the probability that a value of a continuous random variable *X* falls in a particular interval:

$$P[a < X \le b] = \int_{a}^{b} f(x) dx$$

The cumulative distribution function (CDF) F(x) specifies the probability that X is less than some value x:

$$F(x) = P[X < x] = \int_{-\infty}^{x} f(u) du \qquad f(x) = \frac{d}{dx} F(x)$$

• The mean ( $\mu$ ) and variance ( $\sigma^2$ ) are defined as:  $\mu(X) = \overline{X} = E[X] = \int_{-\infty}^{\infty} x \cdot f(x) dx \qquad \sigma^2(X) = E[(x - \overline{X})^2] = \int_{-\infty}^{\infty} (x - \overline{X})^2 f(x) dx$

© Adam Teman, 2020

#### **Remove the Rust: Probability Basics**

#### Normal Random Variables

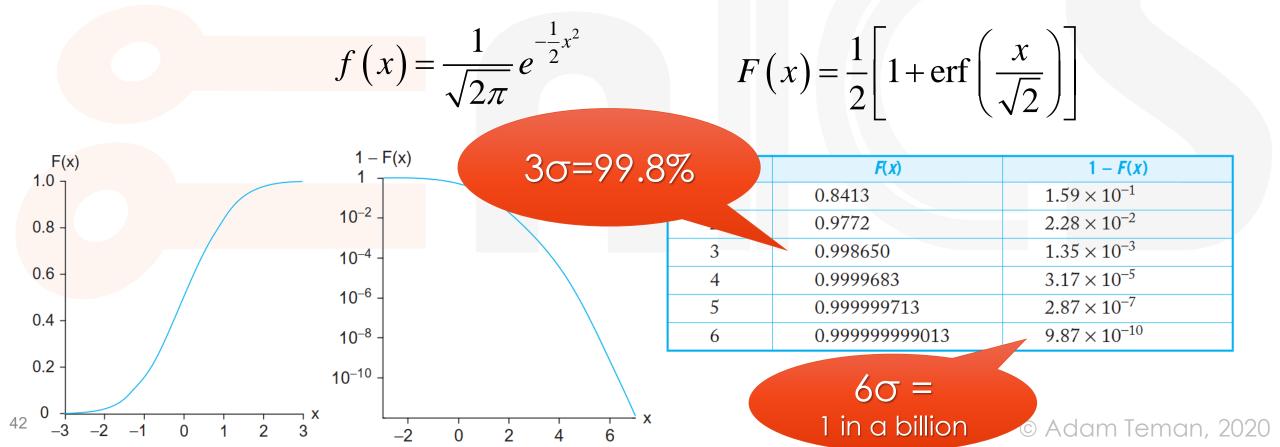

• A normal (Gaussian) random variable, shifted to have a zero mean ( $\mu$ =0) and a normalized standard variation ( $\sigma^2$ =1) has:

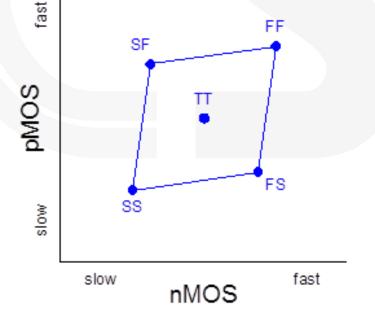

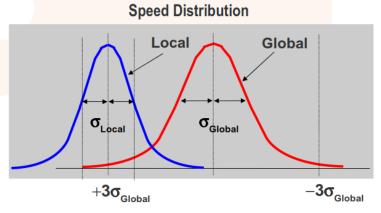

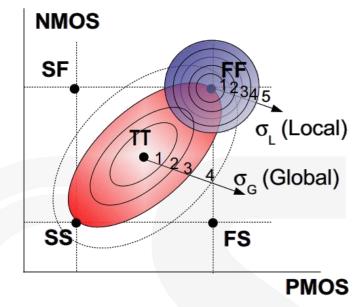

#### **Global Variation Modeling: Process Corners**

#### • Global Variation assumption:

- If a certain process step is *skewed*, the entire chip is affected equivalently.

- We will define "corner cases" of fabrication, i.e.,  $3\sigma$  from the mean.

- We also assume the voltage and temperature are globally affected.

- Devices are modeled for *fast*, *slow* and *nominal* corners.

- Changes in  $V_{\rm T}$ , W, L,  $t_{\rm ox}$

- Devices are tested at various temperatures

- Temperature affects mobility and  $V_{\rm T}$ .

- Typically 0°C 85°C or -40°C 125°C

- Devices are tested at various supply voltages

- Higher voltages cause increased currents

- Typically  $\pm 10\% V_{DD}$

43

© Adam Teman, 2020

#### **Process Corners**

What are the PVT (=Process, Voltage, Temperature) settings for each simulation corner?

| Corner  | V <sub>T</sub> | L <sub>eff</sub> | t <sub>ox</sub> | $V_{DD}$ | T |

|---------|----------------|------------------|-----------------|----------|---|

| Fast    |                |                  |                 |          |   |

| Typical | Х              | Х                | Х               | Х        | Х |

| Slow    |                |                  |                 |          |   |

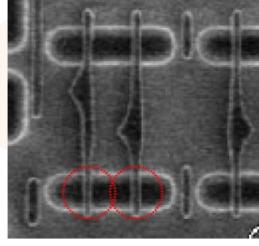

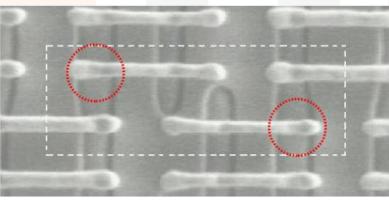

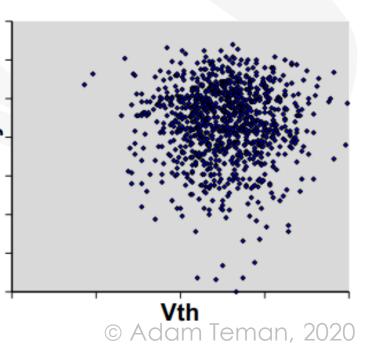

## What about Local Variation?

- Often there are too many parameters to think about and setting a specific corner case is insufficient.

- For example: Pelgrom's Law

- V<sub>T</sub> variance is inversely proportional to transistor area

$$\sigma(V_T) = \frac{K}{\sqrt{W \cdot L}}$$

65nm CMOS NAND cell

Intel 65nm 6T SRAM cell Source: Stanford, EE380

Vth=0.78V 170 Dopants Vth=0.56V

How do we deal with this?

© Adam Teman, 2020

Source: Asenov, IEEE TED 1998

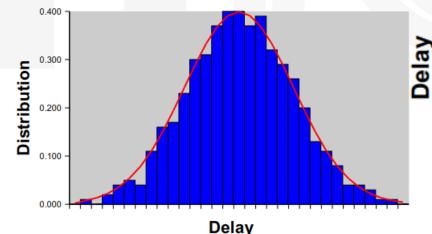

## Monte Carlo Simulation

- The basic approach is to "roll the dice" for each parameter and run a simulation.

- These are called *Monte Carlo* Statistical Simulations.

- The result is a distribution plot of design constraints, e.g., delay or noise margin

- Both Global and Local Variations can be taken into consideration.

Source: Stanford, EE380

#### **Simulation questions**

• How do we plot threshold voltage variation?

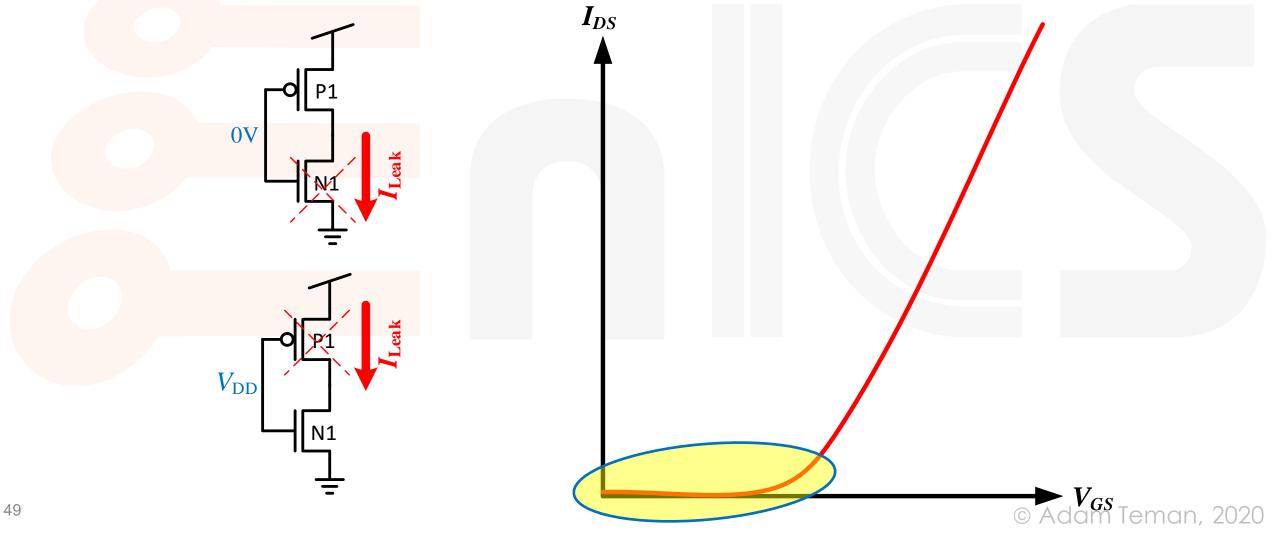

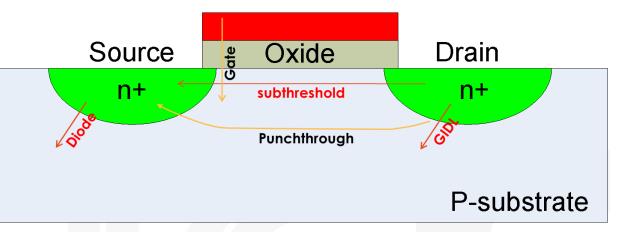

# Leakage in NanoScaled Transistors

### Leakage in Nanoscaled Transistors

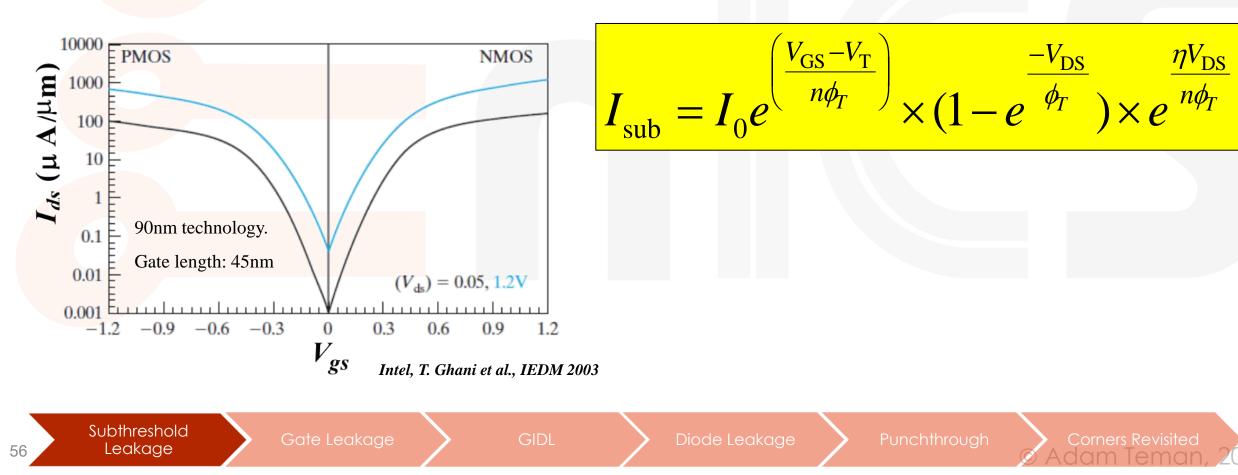

• Transistors that are supposed to be off actually leak!

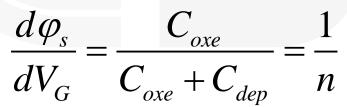

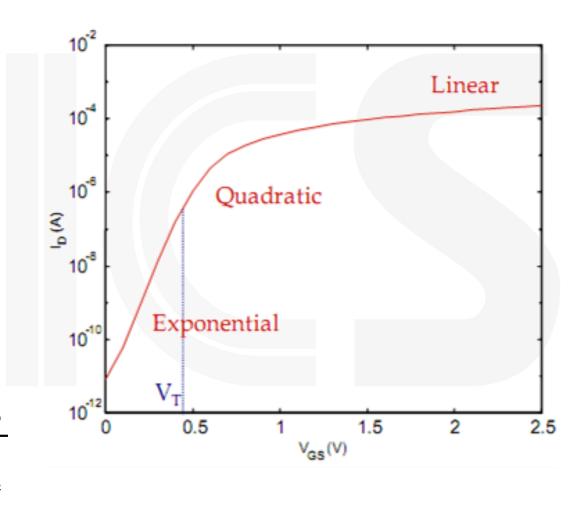

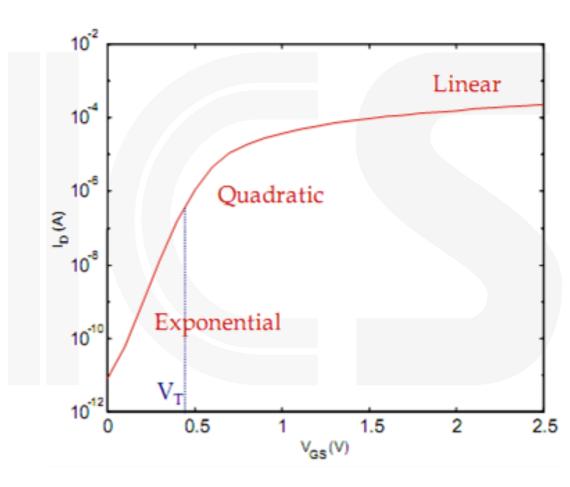

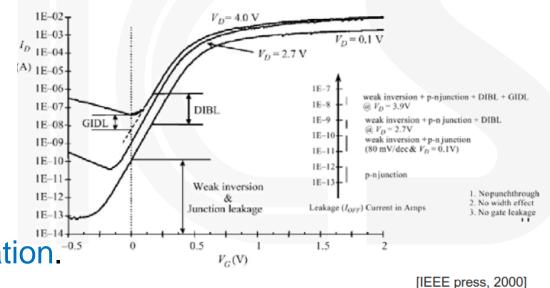

• When  $V_{GS} < V_T$ , there is still a finite carrier concentration at the surface:

$$n_s \propto e^{\frac{\varphi_s}{\phi_T}} \Rightarrow I_{sub} \propto e^{V_{GS} - V_T / n\phi_T}$$

As we saw with the body effect, due to bulk to channel capacitance, the surface voltage isn't only controlled by the gate:

51

GIDL

Diode Leakage

- Let's make things easier:

- Remember that:

$$I_{\rm DS}({\rm sub}) = Const \frac{W}{L} \cdot e^{\frac{V_{\rm GS} - V_{\rm T}}{n\phi_{\rm T}}}$$

And we now defined the threshold voltage according to current:

$$I_{\rm DS}\left(V_{\rm GS}=V_{\rm T}\right)=100\rm{nA}\cdot\frac{W}{L}$$

• So the boundary condition requires:

$$I_{DS}(sub)|_{V_{GS}=V_T} = Const \frac{W}{L} \cdot e^{\sqrt[n]{n\phi_T}} = Const \frac{W}{L} = 100 nA \frac{W}{L}$$

And we can now calculate

subthreshold current as:

$$I_{\rm sub}[nA] = 100 \frac{W}{L} e^{V_{\rm GS} - V_{\rm T}/n\phi_{\rm T}}$$

• An even easier way is to look at the plot of  $log(I_{DS})=f(V_{GS})$ :

- The slope of this curve is called the "Subthreshold Slope"

- The inverse of this slope is known as the "Subthreshold Swing" (S):

$$S \equiv \ln(10)\frac{kT}{q}\left(1 + \frac{C_{dep}}{C_{ox}}\right) = 2.3 \cdot n \cdot \phi_T$$

$$[nA] = 100 \frac{W}{L} e^{V_{GS} - V_T / n\phi_T} = 100 \frac{W}{L} 10^{V_{GS} - V_T / s}$$

• And  $I_{\text{off}}$ , which is defined as the current when  $V_{\text{GS}}=0$  is:  $I_{\text{off}}\left[nA\right] = 100 \frac{W}{L} 10^{-V}$

$$Log (I_{ds})$$

$$V_{ds}=V_{dd}$$

$$V_{ds}=V_{dd}$$

$$I_{off}$$

$$V_{t}$$

$$V_{gs}$$

Corners Revisited

- So subthreshold leakage is:

- Exponentially dependent on  $V_{GS}$ .

- Exponentially dependent on  $V_{\rm T}$ .

- *S* is the subthreshold swing coefficient.

- Optimally,  $S_{opt} = 60 \text{ mV/dec}$

- Realistically  $S \approx 100 \text{ mV/dec}$

$$S \equiv n\phi_T \ln 10 \ge 0.06 \qquad n \equiv 1 + \frac{C_{dep}}{C_{oxe}}$$

54

**Example:**

• We want to design a transistor with:

$$\frac{I_{\rm on}}{I_{\rm off}} \ge 10^4 \qquad S = 60 \frac{\rm mV}{\rm dec}$$

• What is the minimum  $V_{\rm T}$ ?

55

GIDL

2020

### Impact of DIBL

• DIBL causes an additional exponential increase in subthreshold leakage with  $V_{\rm DS}$ .

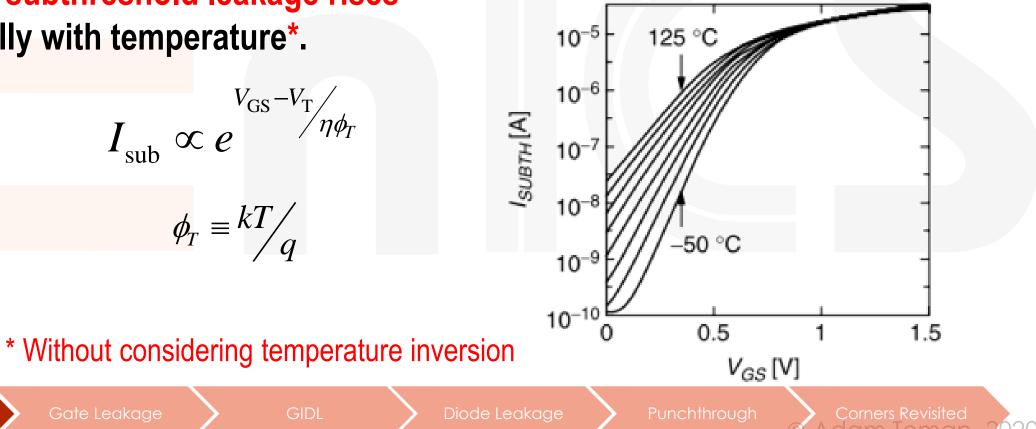

#### **Subthreshold Dependence on Temperature**

- This is rather complex, as mobility degrades with temperature and other device values (such as flatband voltage) are temperature dependent.

- Altogether, subthreshold leakage rises exponentially with temperature\*.

$I_{\rm sub} \propto e^{V_{\rm GS} - V_{\rm T} / \eta \phi_T}$

$\phi_T \equiv kT/q$

GIDL

#### **Temperature Inversion**

• Classic approach to temperature effect on delay:

$$\begin{cases} \propto \mu \\ 1 \\ u = T \\ \infty \end{cases} \rightarrow t_{pd} \propto T \\ So speed decrease \\ with temperature \end{cases}$$

$\left. \begin{array}{c} V_T \stackrel{\mathbf{l}}{\underset{r}{\rightarrow}} T \\ t_{pd} \propto V_T \end{array} \right\} \xrightarrow{\phantom{aaaa}{\phantom{aaaaa}}} t_{pd} \stackrel{\mathbf{l}}{\underset{r}{\rightarrow}} T \\ \begin{array}{c} \mathbf{J} \\ \mathbf{J} \\$

increases with temperature!

- BUT!

- $V_{\rm T}$  decreases by as much as  $-3 {\rm mV/^{\circ}C}$

- The point of *temperature inversion* is the *voltage* at which speed increases with temperature ( $\sim V_{DD} = 1$ V)!

S

GIDL

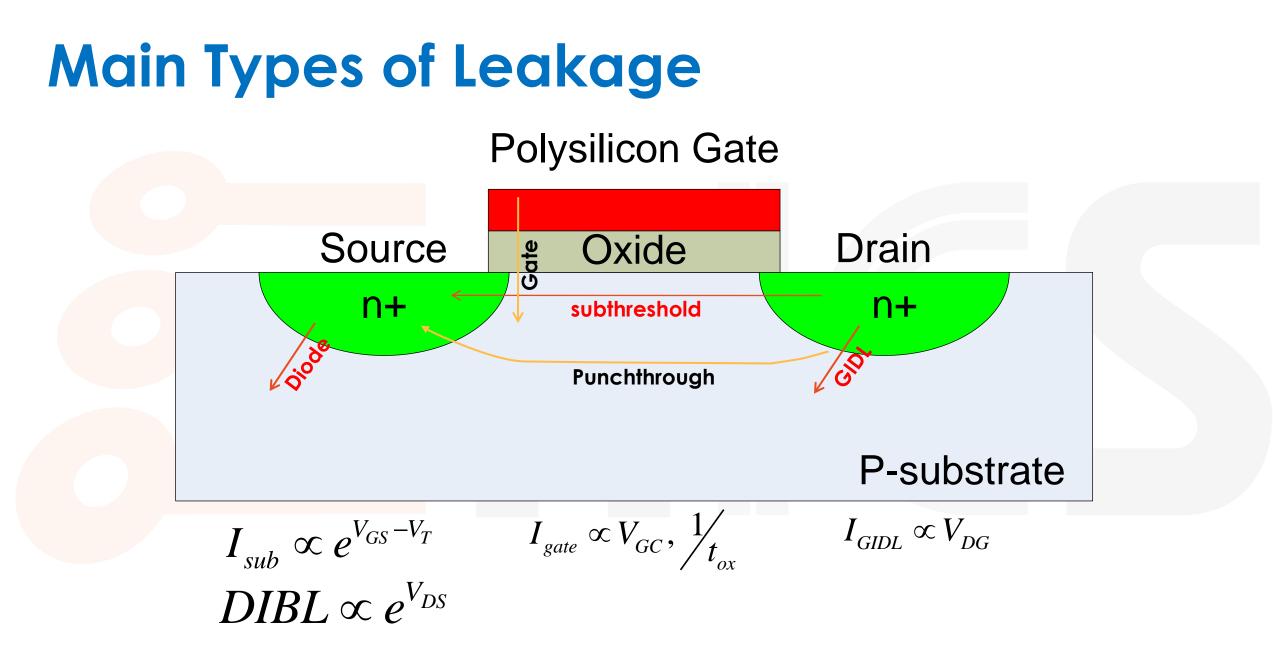

## Gate Leakage

- Two mechanisms:

- Direct tunneling (dominant)

- Fowler Nordheim tunneling

- Exponentially Dependent on:

- Gate Voltage  $(V_G)$

- Oxide Thickness  $(t_{ox})$ .

- Non-dependent on temperature.

- Much stronger in nMOS than pMOS

(higher barrier for holes)

Igate

$E_{\rm ox}$

N + Polv aso lac lado P-sub N+  $10^{-4}$ 15 nm  $= AE_{\rm ox}^2 e^{-B_{\rm e_{\rm ox}}}$  $10^{-6}$ Current density [A/µm2] 20 nm 10<sup>-8</sup>  $10^{-10}$ DD 25 nm 10<sup>-12</sup> OX 30 nm 10<sup>-14</sup> 0.2 0.4 0.6 0.8 1.211.6 1.8 2 0 Applied voltage [v]

• Minimum  $t_{ox}=1.2$  nm!!!

Subthreshold

GIDL

Corners Revisited

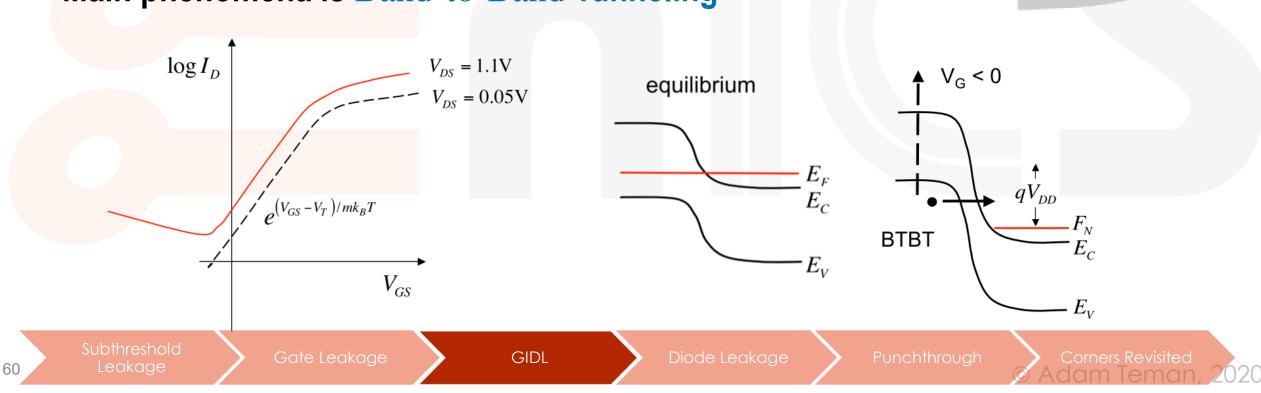

## Gate Induced Drain Leakage

- **GIDL current flows from the drain to the substrate.**

- Caused by high electric field under the gate/drain overlap, causing e-h pair creation.

- Main phenomena is Band-to-Band Tunneling

Gate

Drain

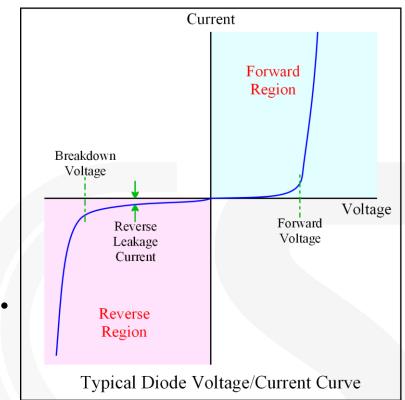

## Diode Leakage

- $J_s = 10-100 \text{ pA}/\mu\text{m}^2 @25^{\circ}\text{C}$  for  $0.25 \mu\text{m}$  CMOS.

- $J_s$  doubles for every 9°C

$$I_{\rm DL} = J_{\rm S} \times A$$

- Much smaller than other leakages in deep sub-micron.

- But a bigger factor in low subthreshold leakage processes, like FinFET.

Source: cmicrotek.com

61

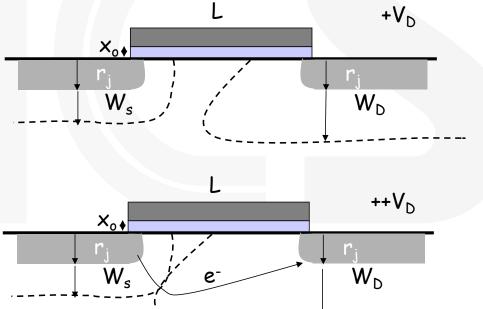

### Punchthrough

- As  $V_{\rm DS}$  grows, so does the drain depletion region, and the channel length decreases.

- In severe cases, the source and drain are connected causing non-controllable leakage current.

Subthreshold Leakage

62

GIDL

Diode Leakage

#### **Polysilicon Gate**

# Leakage Summary

- Subthreshold Leakage:

- $I_{\rm DS}$  >0 when  $V_{\rm GS}$  < $V_{\rm T}$  due to weak inversion.

- Grows with  $V_{\rm GS}$ ,  $V_{\rm DS}$ , lower  $V_{\rm T}$

- Gate Leakage:

- $I_{\rm G}$  >0 due to direct tunneling through the oxide.

- Grows with  $V_{\text{GB}}$ ,  $t_{\text{ox}}$

- Gate Induced Drain Leakage (GIDL):

- $I_{DB}$ >0 due to high electric field in the GD overlap region ( $V_{GD}$ ).

- Reverse Biased Diode Leakage

- I<sub>SB</sub>, I<sub>DB</sub> due to diffusion and thermal generation.

- Punchthrough:

- I<sub>DS</sub> due to drain and source depletion layers touching.

63

GIDL

#### **Process Corners - Revisited**

But what about Temperature Inversion?

• Should we now redefine the PVT settings?

| Corner      | V <sub>T</sub> | $L_{eff}$ | t <sub>ox</sub> | $V_{DD}$ | T |

|-------------|----------------|-----------|-----------------|----------|---|

| Fast        |                |           |                 |          |   |

| Typical     | Х              | Х         | Х               | Х        | Х |

| Slow        |                |           |                 | Ļ        |   |

| Max Leakage |                |           |                 |          |   |

Subthreshold Leakage

64

GIDL

### **Further Reading**

- J. Rabaey, "Digital Integrated Circuits" 2003, Chapters 2.5, 3.3-3.5

- Weste, Harris "CMOS VLSI Design", Chapter 7

- C. Hu, "Modern Semiconductor Devices for Integrated Circuits", 2010, Chapters 4-7

- Tzividis, et al. "Operation and Modeling of MOS Transistor" Chapters 1-5

- E. Alon, Berkeley EE-141, Lecture 9 (Fall 2009)

- M. Alam, Purdue ECE-606 lectures 32-38 (2009) nanohub.org

- A. B. Bhattacharyya "Compact MOSFET models for VLSI design", 2009,

- T. Sakurai, "Alpha Power-Law MOS Model" JSSC Newsletter Oct 2004

- Managing Process Variation in Intel's 45nm CMOS Technology, Intel Technology Journal, 2008

- Berkeley "BSIM 4.6.4 User's Manual"

http://www-device.eecs.berkeley.edu/~bsim/BSIM4/BSIM464/BSIM464\_Manual.pdf