# Digital Integrated Circuits (83-313)

# Lecture 2: The Manufacturing Process

23 March 2020

Disclaimer: This course was prepared, in its entirety, by Adam Teman. Many materials were copied from sources freely available on the internet. When possible, these sources have been cited; however, some references may have been cited incorrectly or overlooked. If you feel that a picture, graph, or code example has been copied from you and either needs to be cited or removed, please feel free to email <u>adam.teman@biu.ac.il</u> and I will address this as soon as possible.

### Lecture Content

| A Process Primer<br>A Process Flow<br>A Process Flow<br>A Process Primer<br>A Quick Introduction to the CMOS Process                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | A Process Primer<br>Detailed Process Variations<br>Detailed Process Flow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Encryptic Section Systems Lates Bar-Ilan University Section Systems Lates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bar-Ilan University<br>Emerging Narcocalid<br>I Desyneted Olicults and Systems Luis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| A Process Primer 2 Detailed<br>Process Nariations 4 Manufacturing<br>Issues<br>Process Variations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1     2     3     4       A Process Primer     Process Flaw     Process Variations     Manufacturing Issues   Manufacturing Issues                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Encos<br>Encoded Second Action of Second | אוניברסיטת בר-איק<br>אוניברסיטת בר-איק |

#### © Adam Teman, 2020

# A Process Primer

A Quick Introduction to the CMOS Process

### Motivation

"I'm exhausted — I just spent all morning writing a note to the milkman!"

I'VE DECIDED TO WRITE A NOVEL ".

1~3 Years...

### Integrated Circuits...

Source: MIT 6.884

© Adam Teman, 2020

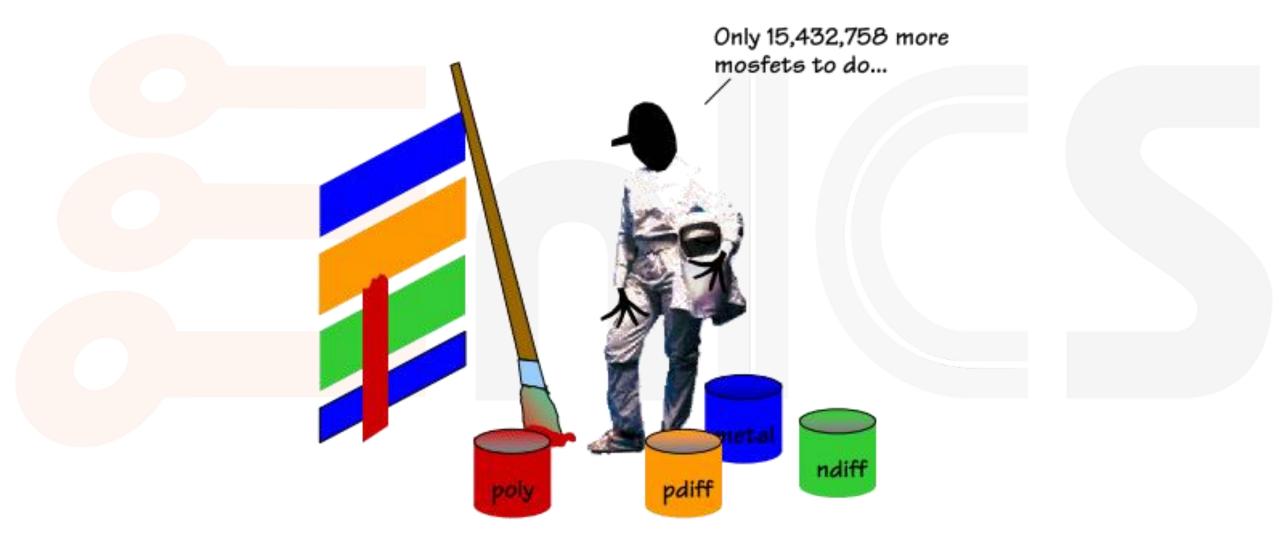

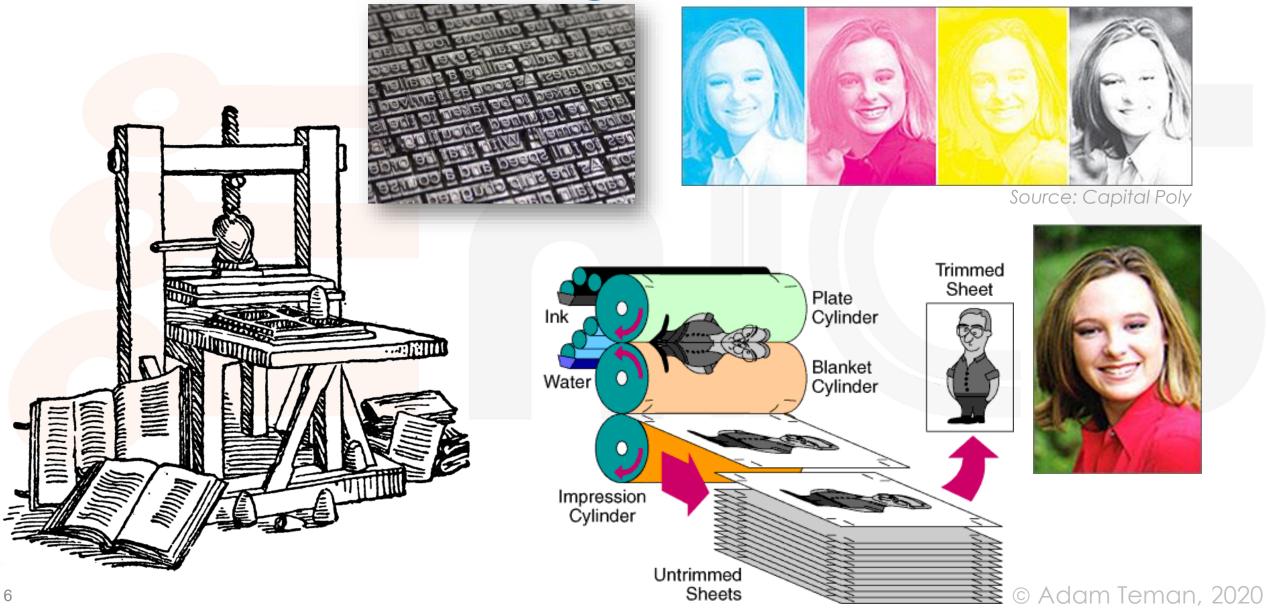

### **Solution: The Printing Process**

### **CMOS Process/Transistors**

© Adam Teman, 2020

### **Basic Process Flow**

### The Computer Hall of Fame

• Speaking of integrated circuits, the first IC-based computer was the Texas Instruments

#### • A molecular electronic computer

Introduced in 1961

- "It performs exactly the same functions as a conventional computer but is **150X smaller and 48X lighter**."

- "Three types of *semiconductor networks* are used in the tiny computers: RS flip-flop, NOR gates, and logic drivers."

- 8-16 "networks" were welded together in a stack.

- A total of 47 stacks (587 "networks") made up the computer.

Source: Texas Instruments

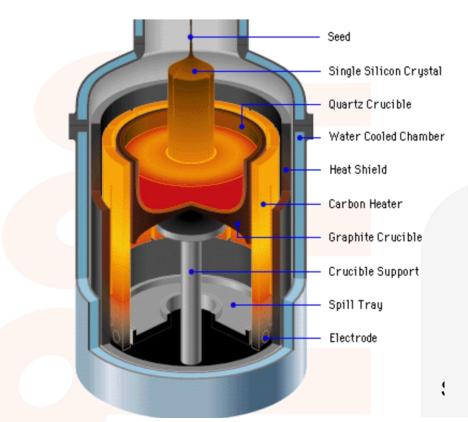

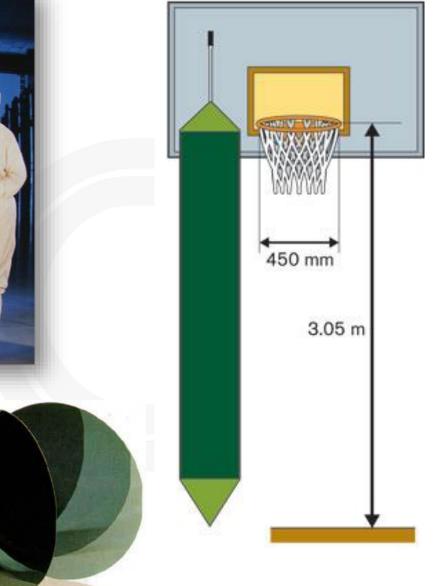

### The Silicon Wafer

99.99999999 % (so-called "eleven nines") !!

Maximum impurity of starting Si wafer is equivalent to 1 mg of sugar dissolved in an Olympic-size swimming pool.

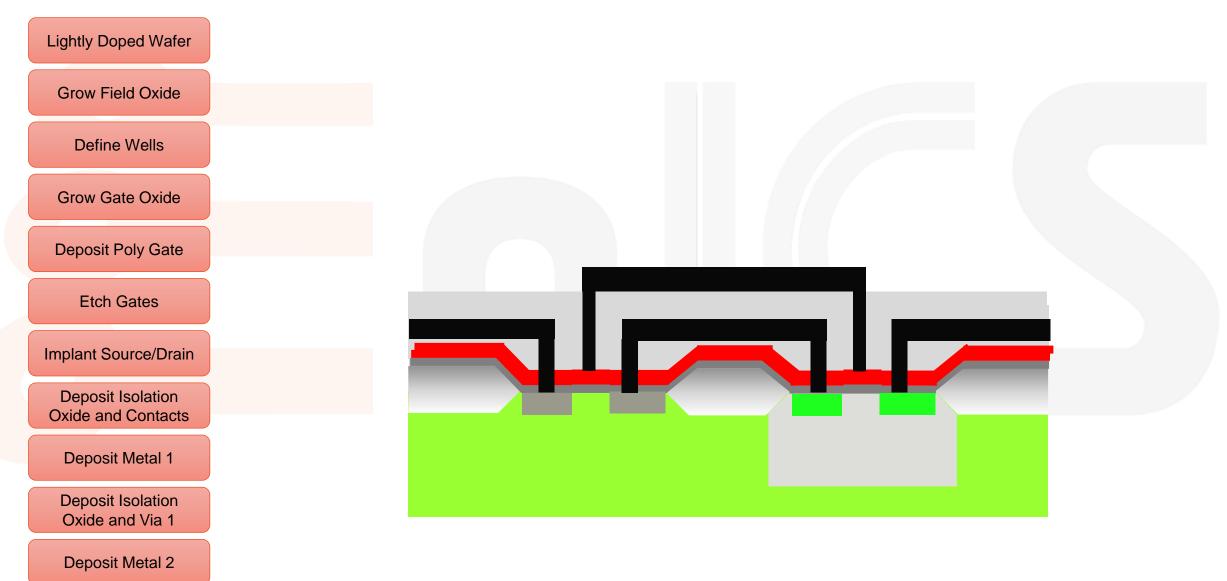

Lightly Doped Wafer

12

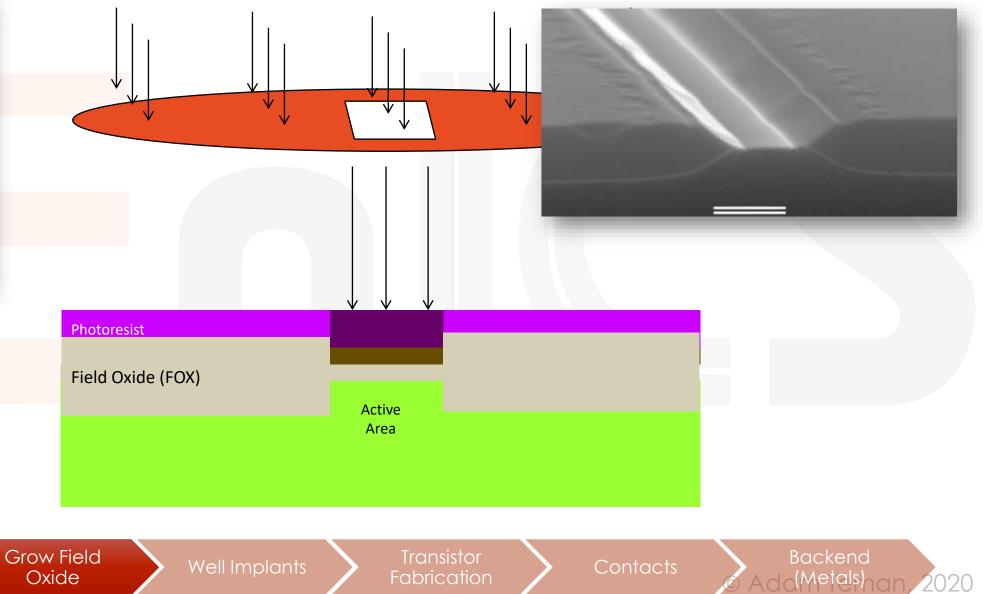

Grow Field Oxide

Well Implants

Transistor Fabrication

Smithsonian (2000)

Contacts

Backend Ada(Metals)<sub>han,</sub>

2020

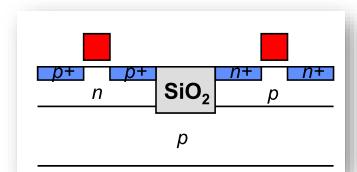

### Field Oxide – The LOCOS Process

Lightly Doped

Wafer

### Field Oxide – The STI Process

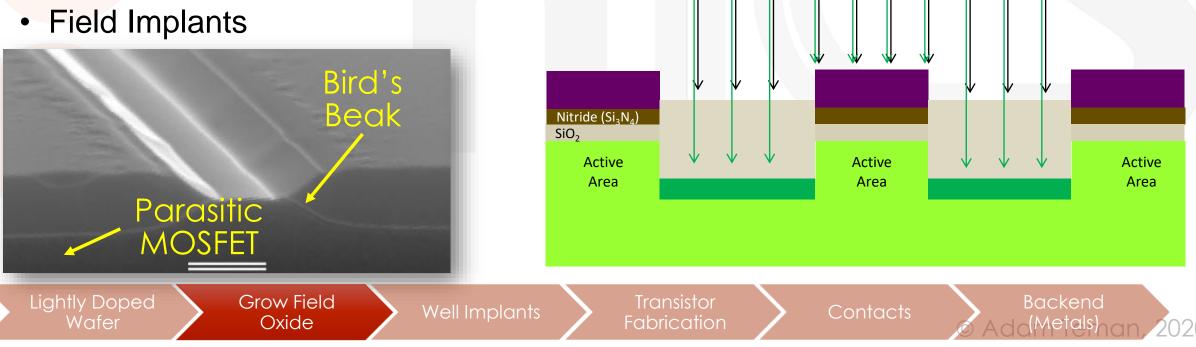

- The LOCOS Process has two problems:

- Bird's Beak makes it hard to make transistors close to each other.

- A parasitic MOSFET can turn on underneath the FOX.

### • Solution:

14

Shallow Trench Isolation (STI)

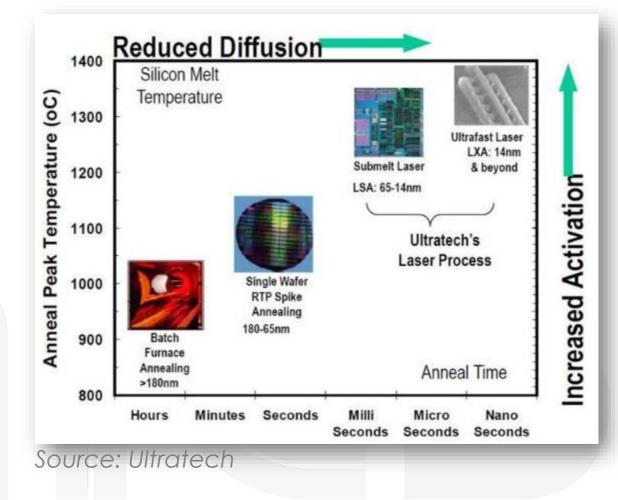

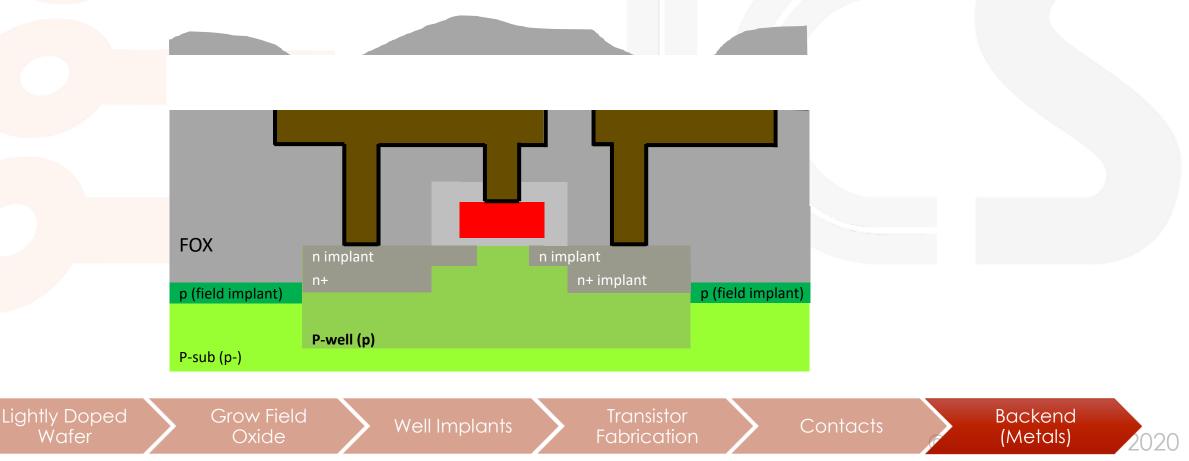

### Well Implantation

- Cover wafer with thin layer of oxide.

Implant wells through photolithographic process.

- After implant we must Anneal to the covalent bonds, and Diffuse to get the wells to the depth we want.

- <u>Annealing</u>: Heating up the wafer to fix covalent bonds. Done after every ion implantation or similar damaging step.

- <u>Diffusion</u>: Movement of dopants due to heating of the wafer. Usually this is unwanted, as it changes the doping depth.

Lightly Doped

Wafer

Well Implants

Transistor Fabrication Backend

(Metals)

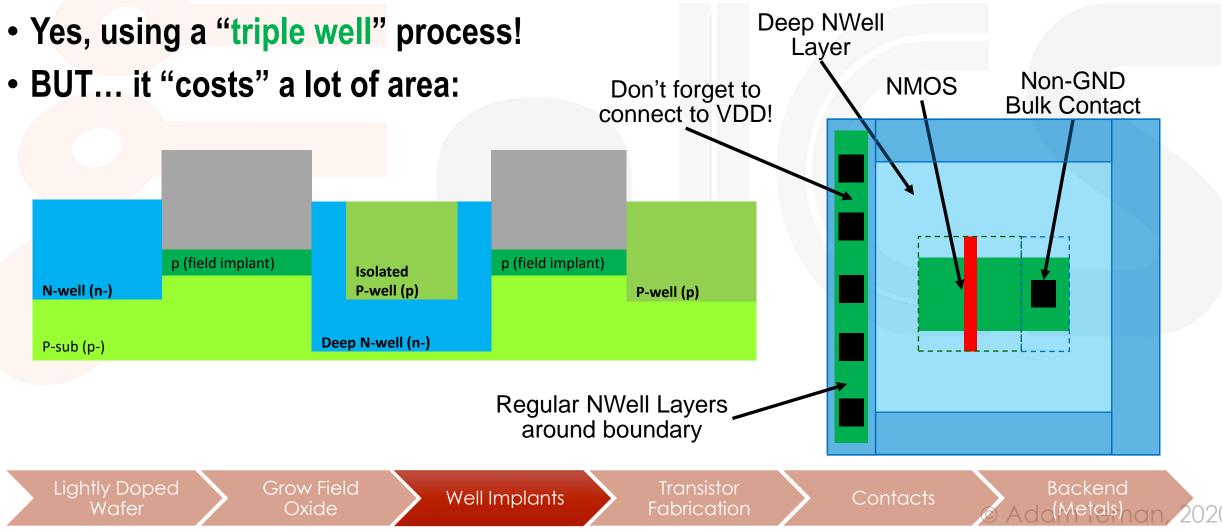

### Well Implantation – Deep N-Wells

Can we change the body voltage of an nMOS transistor?

16

### Transistor Fabrication: V<sub>T</sub> Implant

• The threshold voltage of a transistor is approximately:

$$V_T = V_{FB} + 2\phi_f + \frac{\sqrt{2\varepsilon_s q N_A \left(2\phi_f\right)}}{C_{ox}} + \frac{q Q_I}{C_{ox}}$$

- So the first step is to implant  $Q_I$ .

- Random Dopant Fluctuations (RDF) cause a problematic distribution in  $V_{\rm T}$  between devices.

- Native Transistors are transistors that didn't go through this step (i.e.  $V_{\rm T} \approx 0 \rightarrow$  Depletion)

Lightly Doped

Wafer

Well Implants

Backend

(Metals)

### Ion Implantation

18

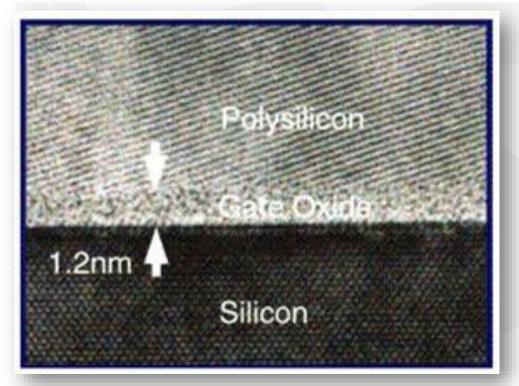

### **Transistor Fabrication: Gate Oxide**

Well Implants

• Gate Oxide thickness ( $t_{ox}$ ) is one of the most important device parameters.

Transistor

Fabrication

- 45nm technology has a 1.2nm thick layer (about 5 atoms!).

- Gate oxide growth has to be done in super-clean conditions to eliminate traps and defects.

Grow Field

Oxide

• High-K materials extremely complicate this process.

Contacts

Backend

Metals)

Lightly Doped

Wafer

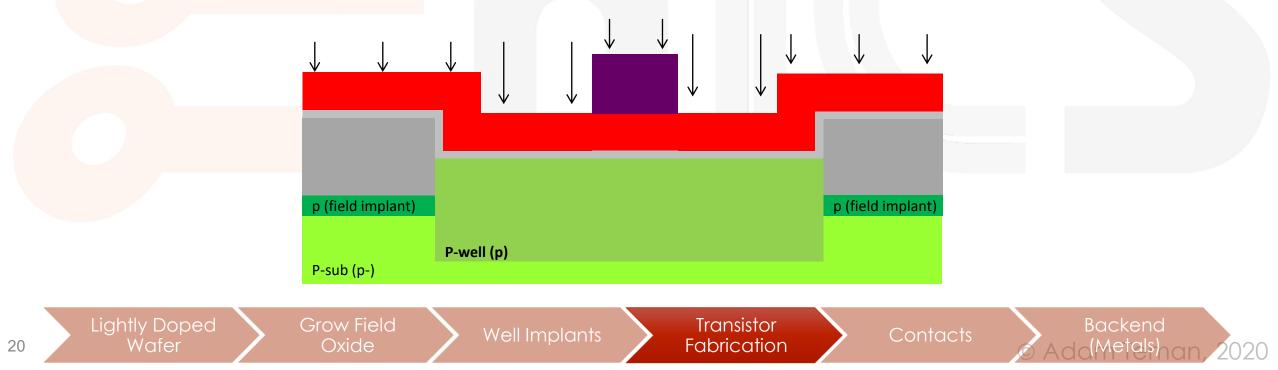

### **Transistor Fabrication: Gate Etch**

- Originally Aluminum was used as the gate material, then polysilicon, now metal again.

- The gate is the smallest dimension that is fabricated through photolithography.

- The oxide is self-aligned to the gate through the etching process.

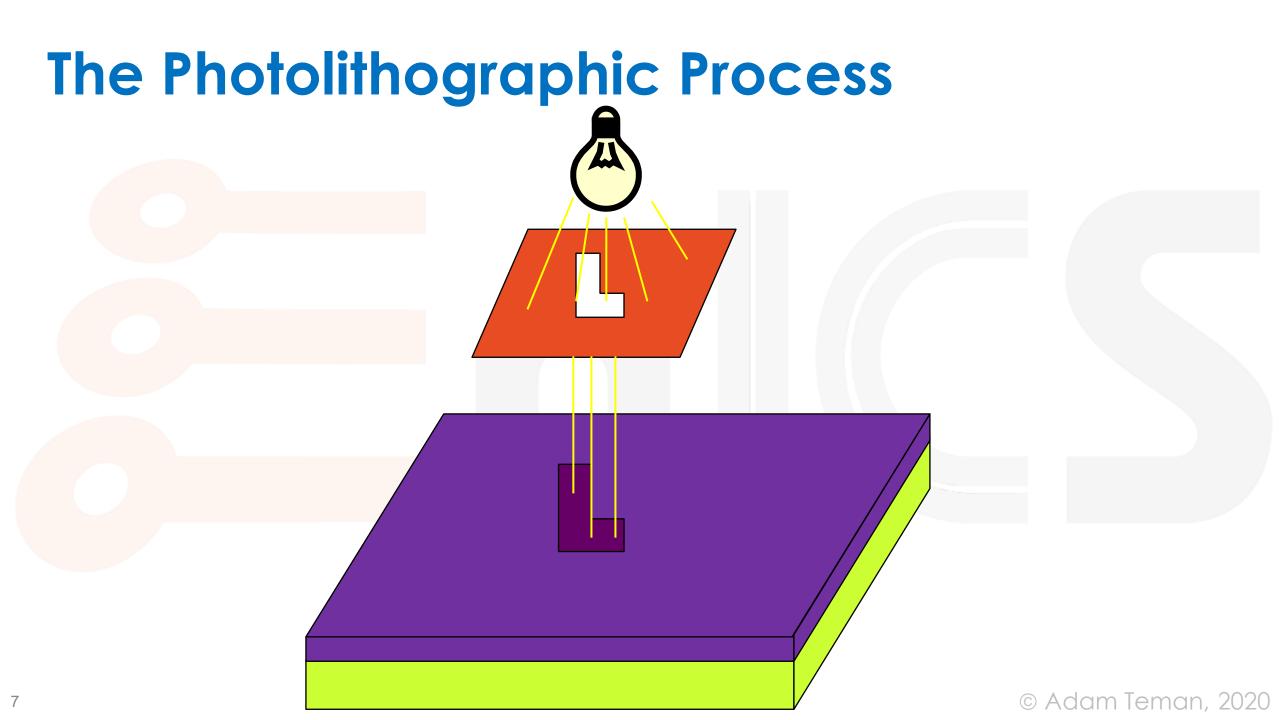

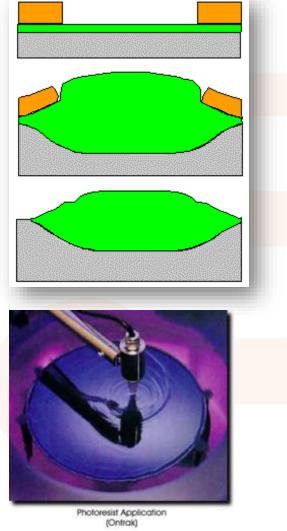

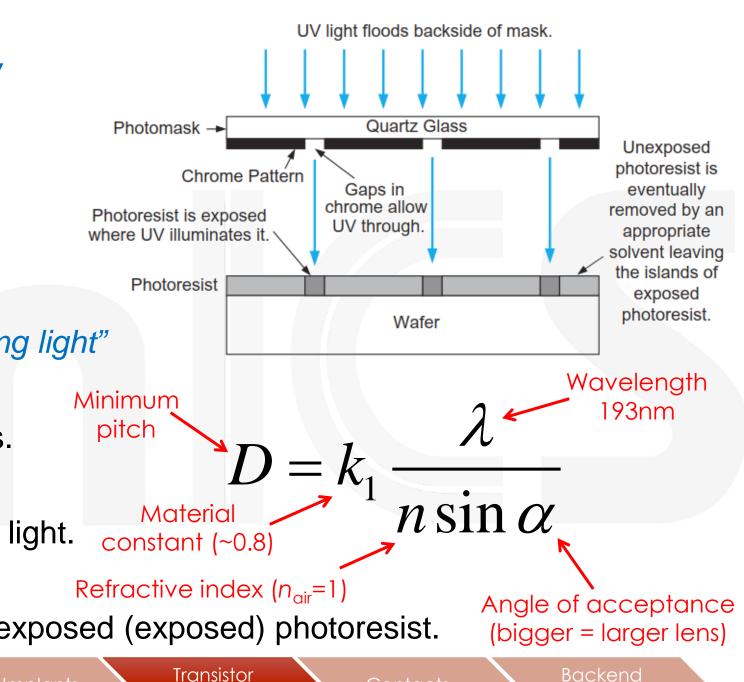

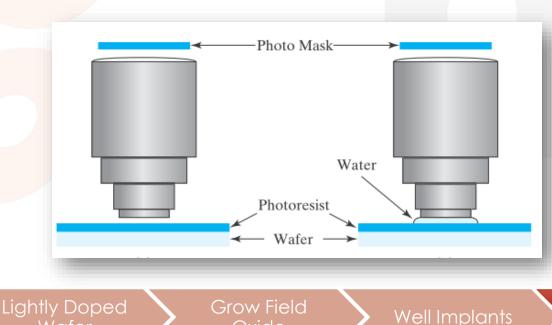

## **Photolithography**

- From Greek:

- photo light

- *lithos* stone

- graphe picture

- "carving pictures in stone using light"

- Photomask (reticle):

- Chrome covered quartz glass.

- Photoresist:

- Organic material, sensitive to light.

Grow Field

Oxide

• Developer:

Lightly Doped

Wafer

Fabrication

Well Implants

Contacts

(Metals)

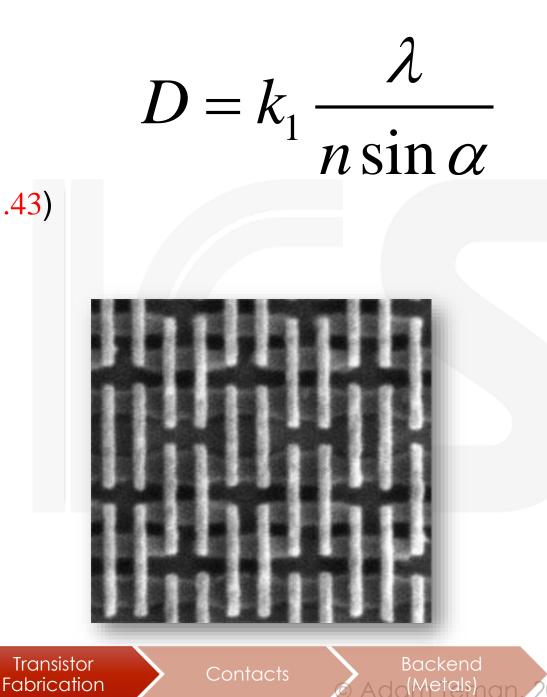

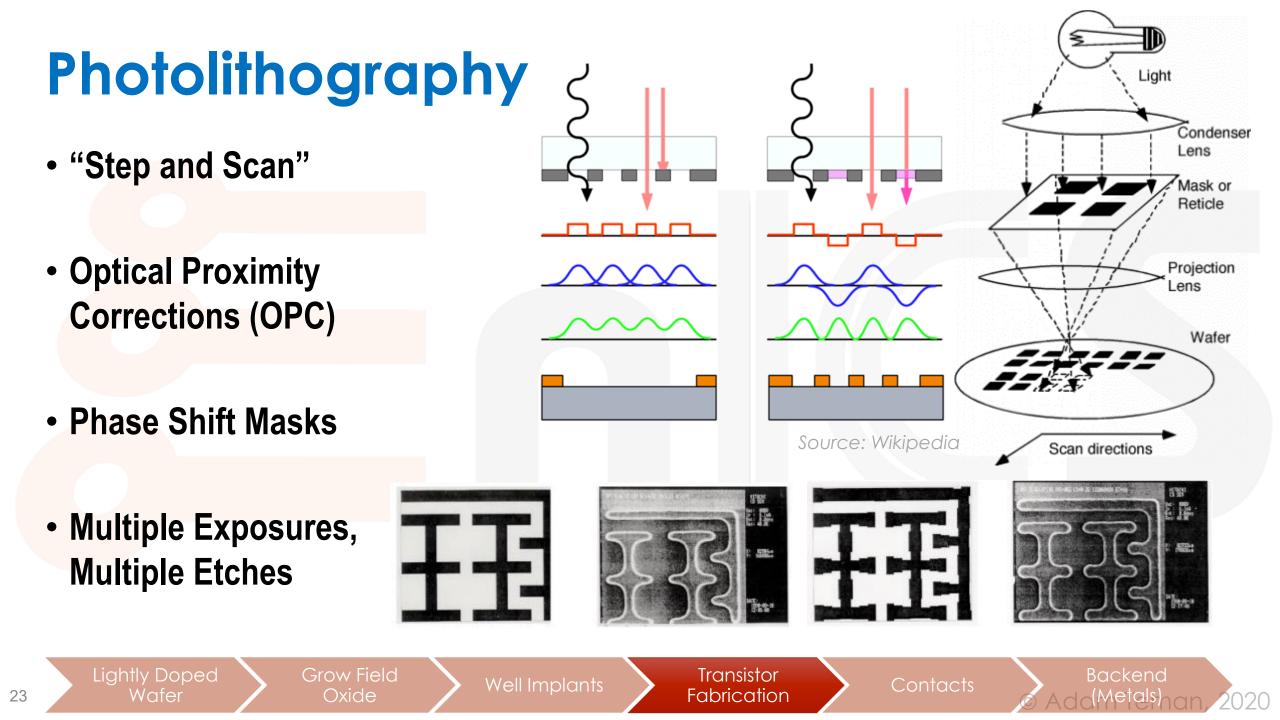

### Photolithography

#### • Resolution Enhancement Techniques:

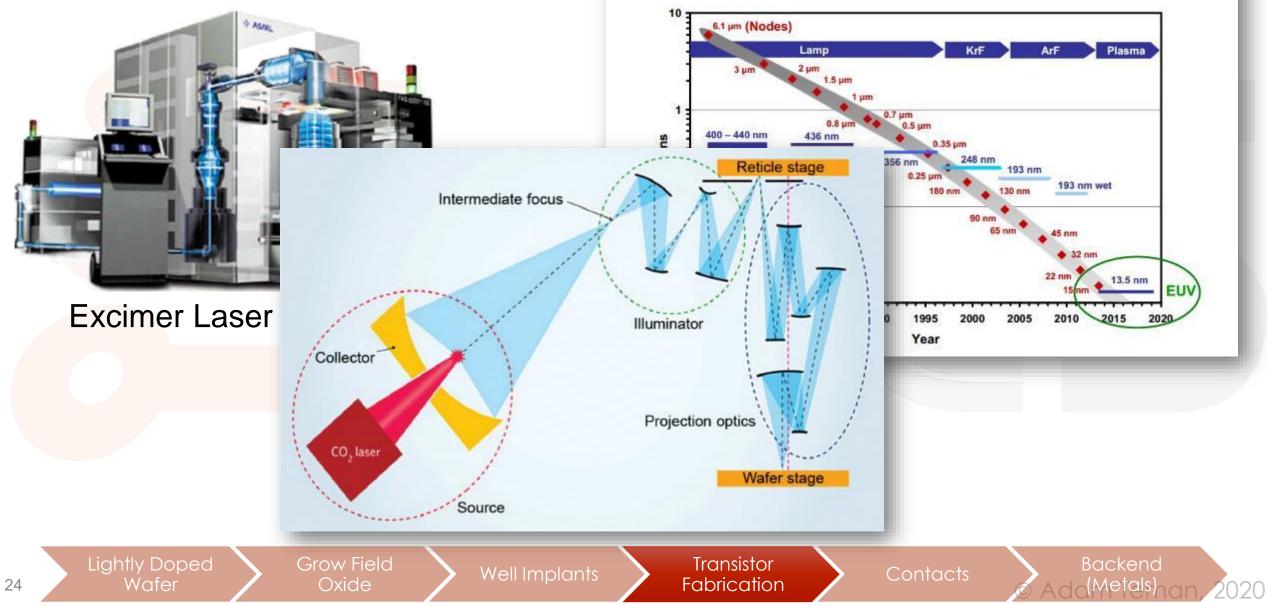

- Use *immersion* (wet) lithography ( $n_{water} = 1.43$ )

- Use mask and layout techniques

- Use a smaller wavelength (193 nm).

- From 7nm (7+), EUV (13 nm) is used.

Oxide

Wafer

### Photolithography

#### Lithography scaling

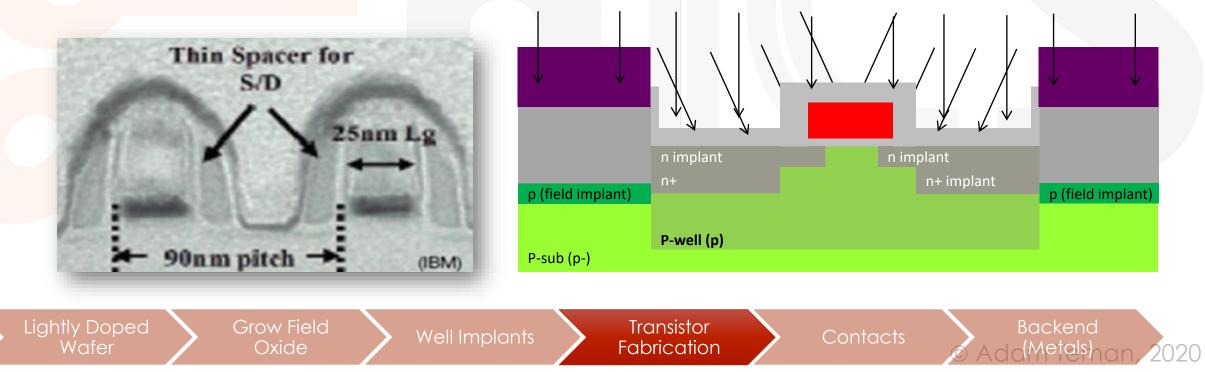

### **Transistor Fabrication: Tip Extension**

- For various reasons, we need a Lightly Doped Drain (LDD).

- But for source/drain resistance, we need a heavily doped area away from the channel.

- Therefore, a *Tip* or *Spacer* is formed:

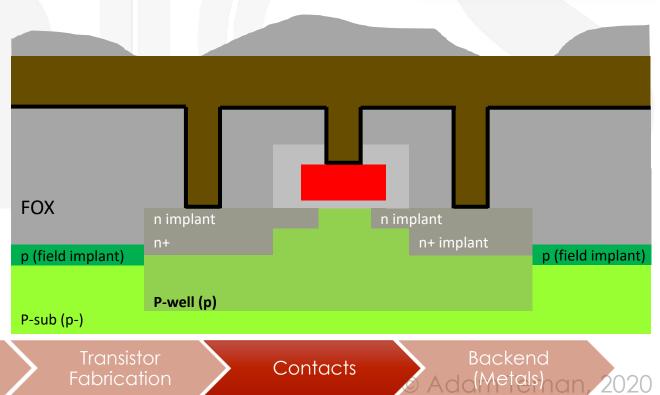

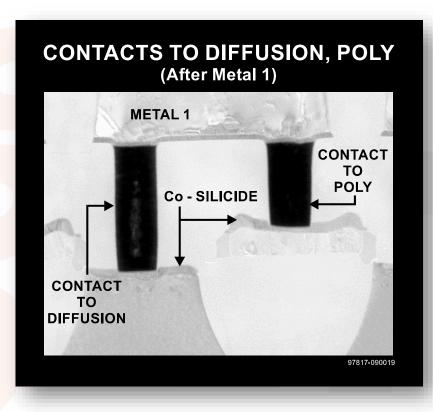

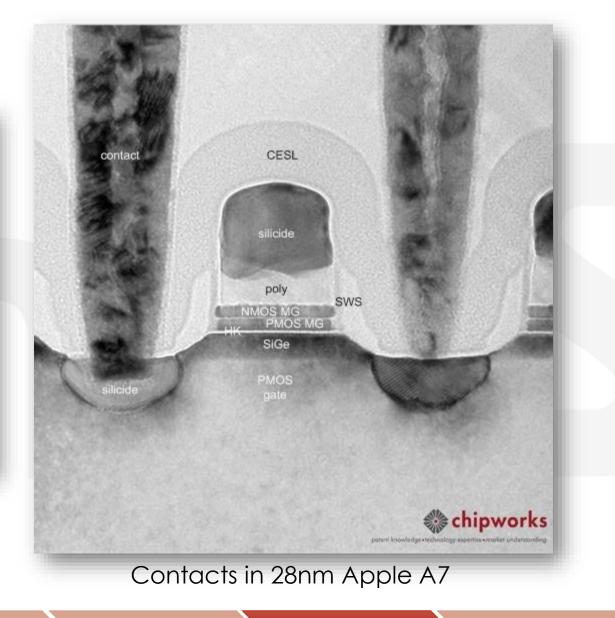

### **Contacts – Damascene Process**

Well Implants

#### • The Damascene Process is used to make contacts/vias

- A thick isolation oxide is grown.

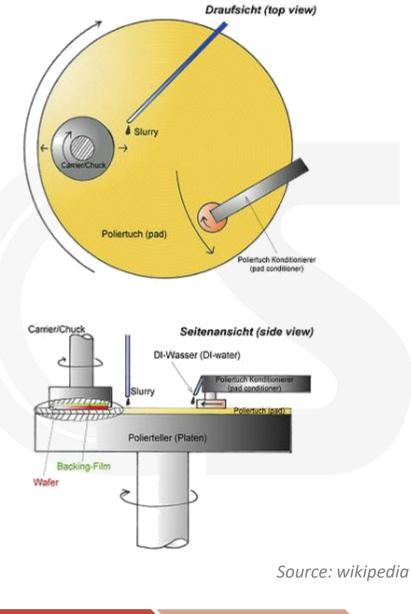

- The bumpy oxide is planarized through Chemical-Mechanical Polishing (CMP)

Grow Field

Oxide

- Contacts are etched, lined and plugged.

- The remaining metal is etched away.

Lightly Doped

Wafer

### Contacts

Lightly Doped Wafer

Grow Field Oxide

Well Implants

Transistor Fabrication

Contacts

Backend Add(Metals)han

2020

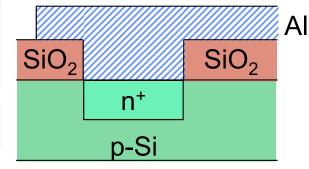

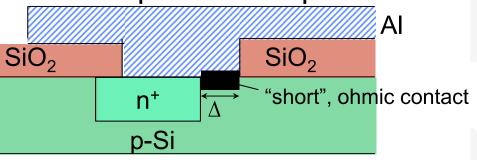

### **Misalignment Problems**

#### goal: contact to diffusion

28

problem: misalignment between process steps

solution: make diffusion larger than contact (overlap)

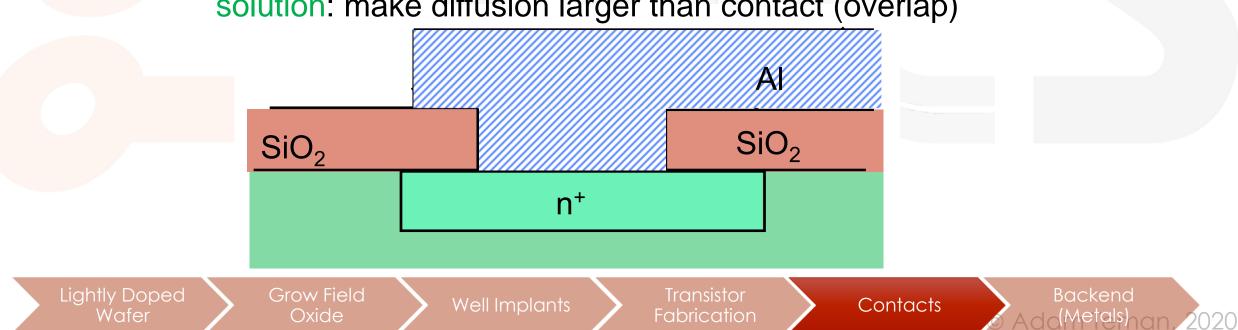

### Planarization

Planarization is achieved with Chemical-Mechanical Polishing (CMP)

29

Grow Field Oxide

Well Implants

Transistor Fabrication Backend (Metals)nan, 2020

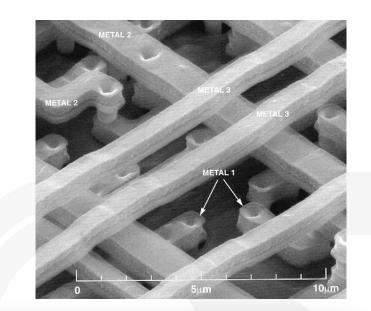

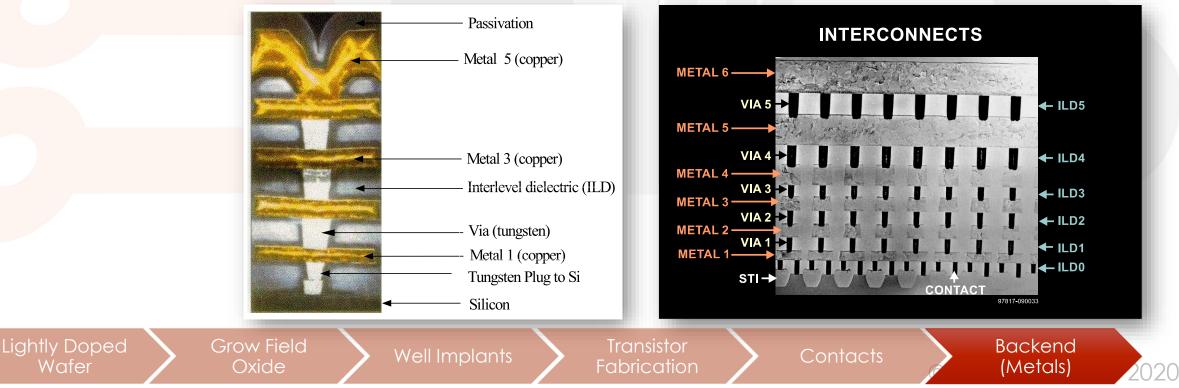

### Metal Layers (Backend)

- ILD = Inter-layer Dielectric (low-*k*)

- Passivation protects the final layer

- Al or Cu for Metal layers

30

W for Plugs, TiN for barrier layer

### **Copper Interconnect**

- Copper cannot be deposited directly on S<sub>i</sub>O<sub>2</sub>

- To solve this, the dual-Damascene process was introduced.

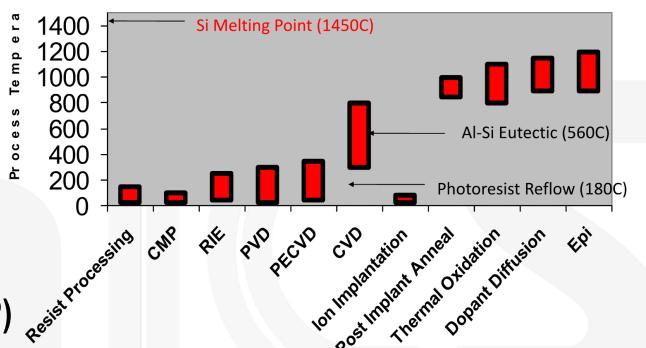

### **Microfabrication Summary List**

- Lithography

- Thermal Oxidation

- Etching

- Ion Implantation

- Epitaxial Growth (PECVD)

- Chemical Mechanical Polishing (CMP)

**Grow Field**

Oxide

Deposition (Physical Vapor Deposition PVD, Chemical Vapor Deposition CVD)

Transistor

Fabrication

Diffusion (Furnace Annealing, Rapid Thermal Annealing RTA)

Well Implants

Metal Plating

**Lightly Doped**

Wafer

Others...

Contacts

Backend

(Metals)

### **Process Variations**

- Variation can occur at different levels:

- Fab to Fab variation

- Lot to Lot variation

- Wafer to Wafer variation

- Die to Die Variation

- Device to Device Variation

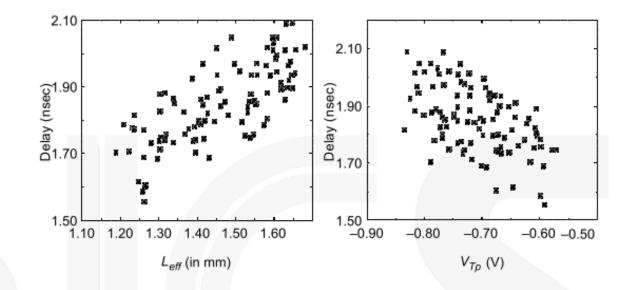

- Process Parameters

- Such as impurity concentrations, oxide thickness, diffusion depth.

LER/LWR

WPE

- Caused during Deposition and Diffusion steps.

- Affect  $V_{\rm T}$  and  $t_{\rm ox}$ .

- Device Dimensions

Types of

Variation

Lengths and widths of gates, metals, etc.

RDF

• Caused due to photolithographic limitations.

Delay of Adder circuit as a function of variations in L and  $V_T$

Additional Variations

Impact of Ad Variation

34

### **Types of Process Variation**

#### • Random Variation:

Occurs without regards to the location and patterns of the transistors within the chip (e.g., RDF)

Additional

Variations

Impact of

ariation/

For example – Random Dopant Fluctuation (RDF)

#### Systematic Variation:

Related to the location and patterns

• For example – layout density, well-proximity, distance from center of wafer

LER/LWR

WPE

### Intra-die (Within-die) Variations

Variations between elements in the same chip

RDF

• A.k.a. - "Local Variation"

### Inter-die (Die-to-Die)

Types of

Variation

Variations between chips in the same wafer or in different wafers

• A.k.a. - "Global Variation"

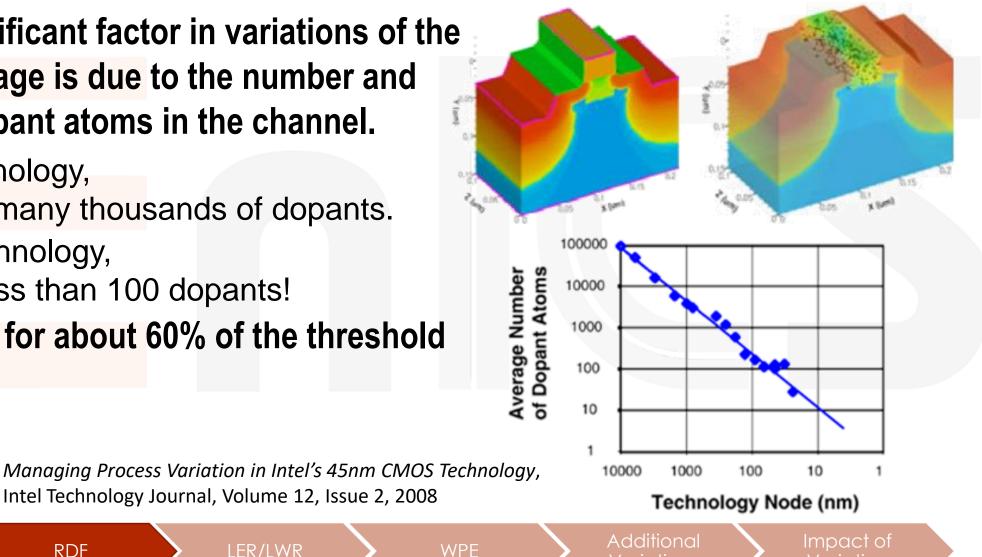

### **Random Doping Fluctuation (RDF)**

Intel Technology Journal, Volume 12, Issue 2, 2008

LER/LWR

- The most significant factor in variations of the threshold voltage is due to the number and location of dopant atoms in the channel.

- In 1µm technology, there were many thousands of dopants.

- In 32 nm technology, there are less than 100 dopants!

RDF

RDF accounts for about 60% of the threshold variation.

/ariation

Variations

Types of

Variation

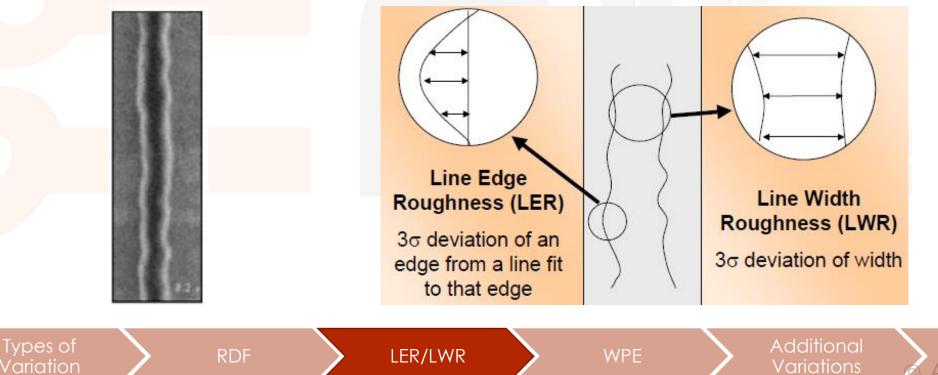

### Line Edge/Width Roughness (LER/LWR)

- Line Edge Roughness (LER) and Line Width Roughness (LWR) cause changes in sub-threshold current and threshold voltage.

- These problems are expected to surpass RDF as the main cause of variations at deep nanoscale technologies.

37

Impact of

Variation

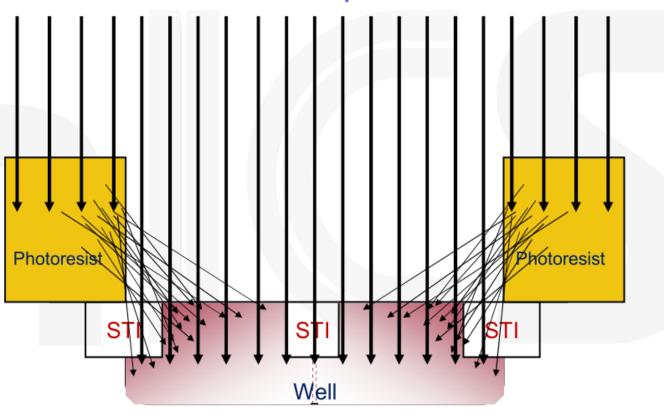

# Well Proximity Effects (WPE)

Threshold voltage depends on distance to well edge.

Well Ion Implant

#### http://www.solidodesign.com/

Impact of

Variation

2020

38

LER/LWR

**WPE**

Additional Varia<u>tions</u>

# **Additional Variations**

#### Gate Dielectric Variation

- Oxide Thickness

- Fixed Charge

- Defects and Traps

- CMP Variations

- STI Steps

- Metal Gate height

- ILD (Insulation Layer Dielectric) and Interconnect Thickness

Additional

Variations

WPE

Impact of

'ariation

- Strain Variation

- Implant Variation

Types of

Variation

• Rapid Thermal Anneal (RTA) Variation

RDF

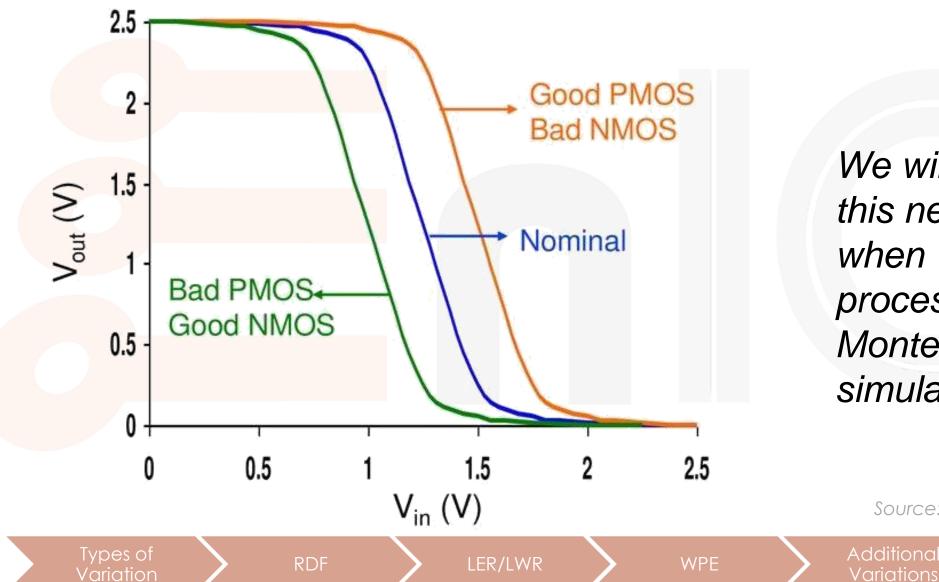

### **Impact of Process Variations**

We will get back to this next lecture when we discus process corners and Monte Carlo simulation...

Source: Rabaey, et. al.

Impact of

Variation

020

40

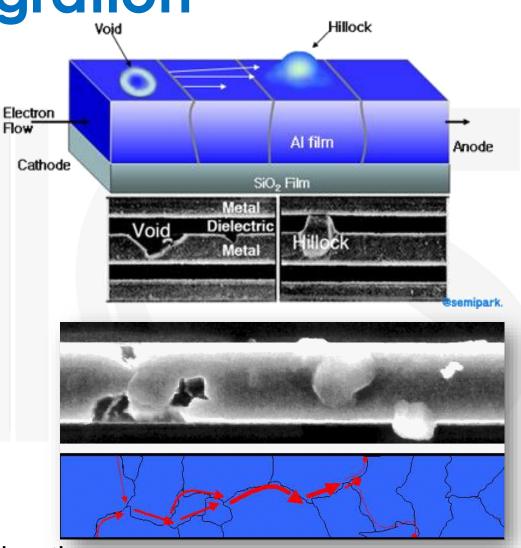

### **Hillocking and Electromigration**

### • Hillocking:

- The development of small "hills" in the interconnect due to stress on the Aluminum.

- Can short between metal layers, crack SiO<sub>2</sub>, cause bumpiness.

- Adding Cu to A1 helps reduce hillocking.

### • Electromigration:

- Movement of Aluminum atoms due to high current densities that can eventually cause hillocks (shorts) or voids (opens).

- Proper design (keep J [A/cm<sup>2</sup>] under a limit) helps prevent electromigration.

- Cu interconnect is very efficient against electromigration.

42

Density

Latchup

#### © Adam Teman, 2020

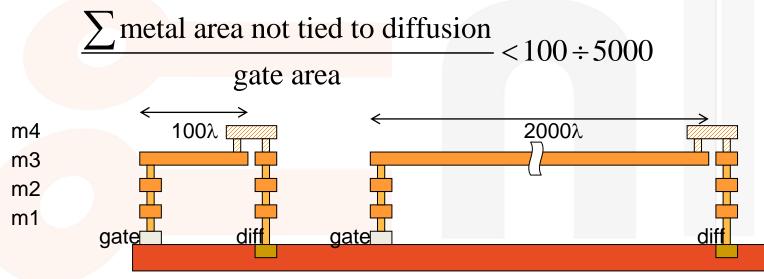

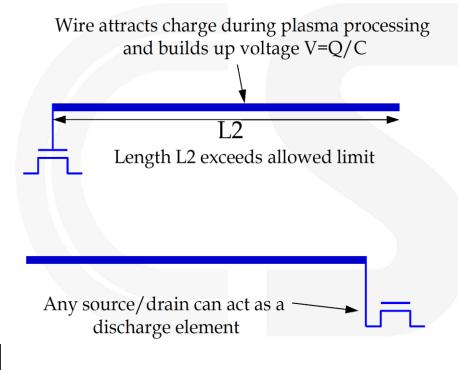

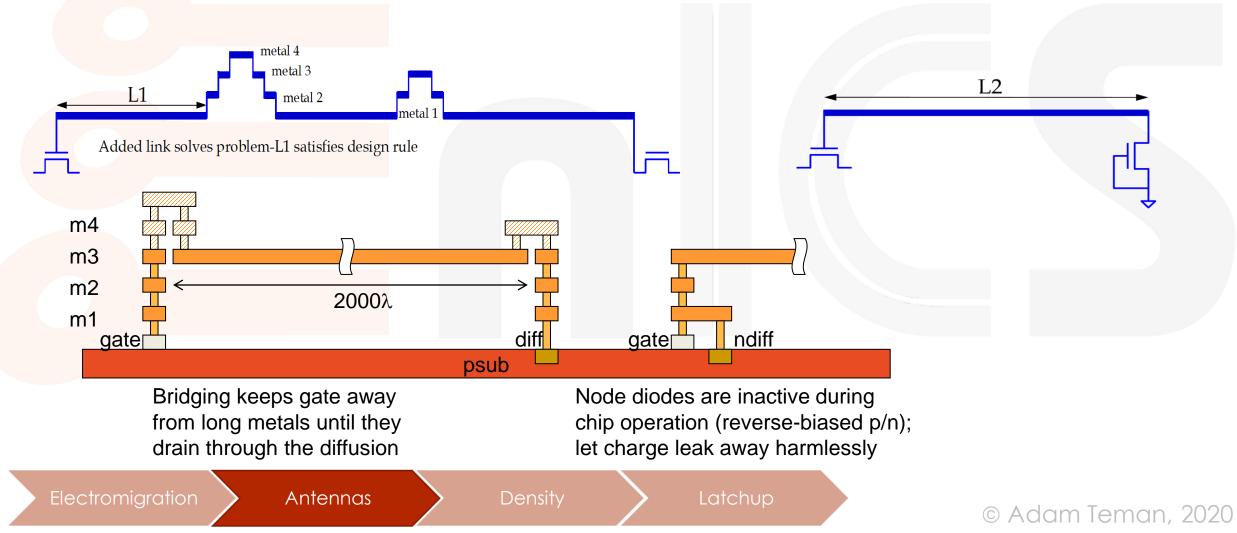

### Antenna Effect

- Charge is built up on interconnect layers during deposition.

- If enough charge is created, this can cause a high voltage to breakdown the thin gates.

Safe: m3 is too short to accumulate very much charge; won't kill gate Dangerous: lots of m3; will probably accumulate lots of charge and then blow oxide

43

Density

Latchup

### Antenna Effect

• "Bridging" or "Antenna Diodes" are used to eliminate the Antenna Effect.

44

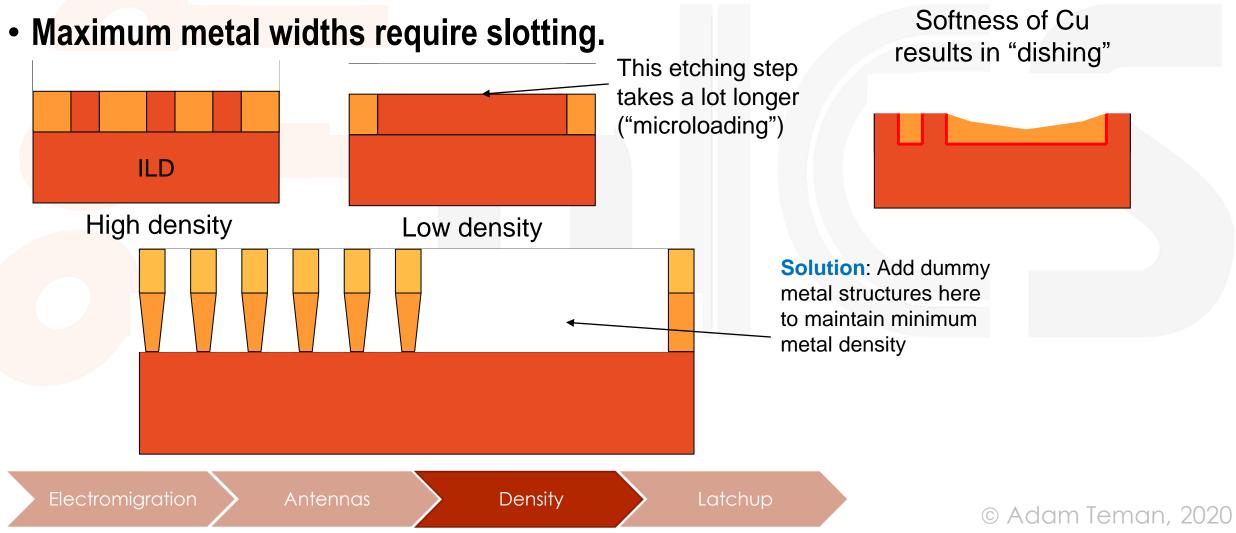

### Layer Density

45

• Metal layers should have between ~30% to ~70% density.

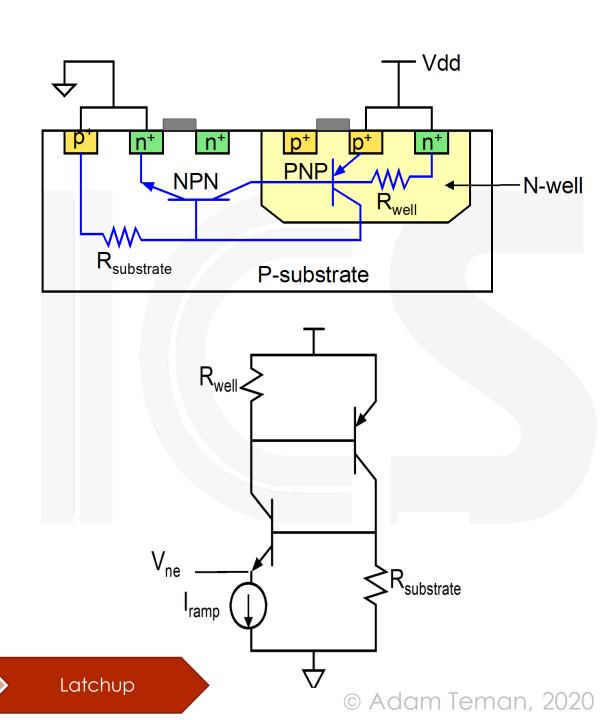

### Latchup

- The multiple n-type and p-type regions in the CMOS process create parasitic BJT transistors.

- Unintentional "Thyristors" can turn on and short  $V_{\rm DD}$  and GND.

- This requires power down at the least, and sometimes causes chip destruction.

• To reduce the risk of latchup, distribute well/substrate contacts across the chip.

46

Density

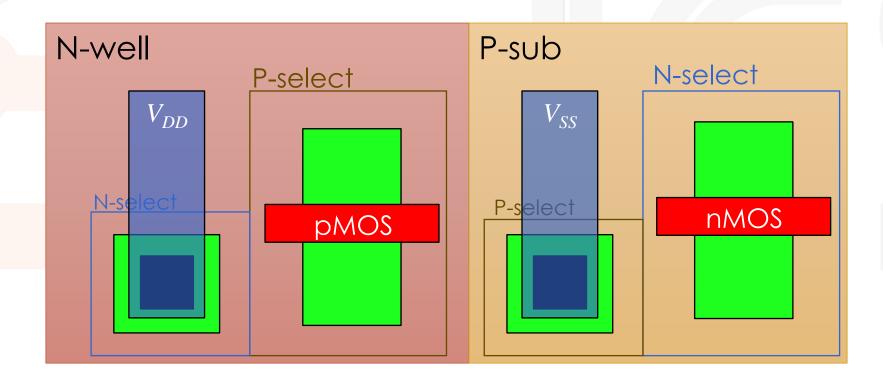

### **Bulk Contacts**

47

To ensure a constant body voltage across large areas, Bulk Contacts or Taps have to be added frequently.

© Adam Teman, 2020

### **Further Reading**

- J. Plummer "Silicon VLSI Technology", 2000 especially Chapter 2

- J. Rabaey, "Digital Integrated Circuits" 2003, Chapters 2.2-2.3

- C. Hu, "Modern Semiconductor Devices for Integrated Circuits", 2010, Chapter 3 http://www.eecs.berkeley.edu/~hu/Book-Chapters-and-Lecture-Slides-download.html

- E. Alon, Berkeley *EE-141*, Lectures 2,4 (Fall 2009) http://bwrc.eecs.berkeley.edu/classes/icdesign/ee141\_f09/

- Berkeley EE-143 (Lectures Nguyen 2014, Slides Cheung 2010)

- Tel Aviv University Yosi Shacham