# Digital Microelectronic Circuits (361-1-3021)

Presented by: Mr. Adam Teman

Lecture 8: Ratioed Logic

1

**Digital Microelectronic Circuits**

### Motivation

- □ In the previous lecture, we learned about *Standard CMOS Digital Logic* design.

- CMOS is unquestionably the leading design family in use today, do to its many advantages and relative simplicity. However, it has a number of drawbacks that have led to the development of alternative solutions.

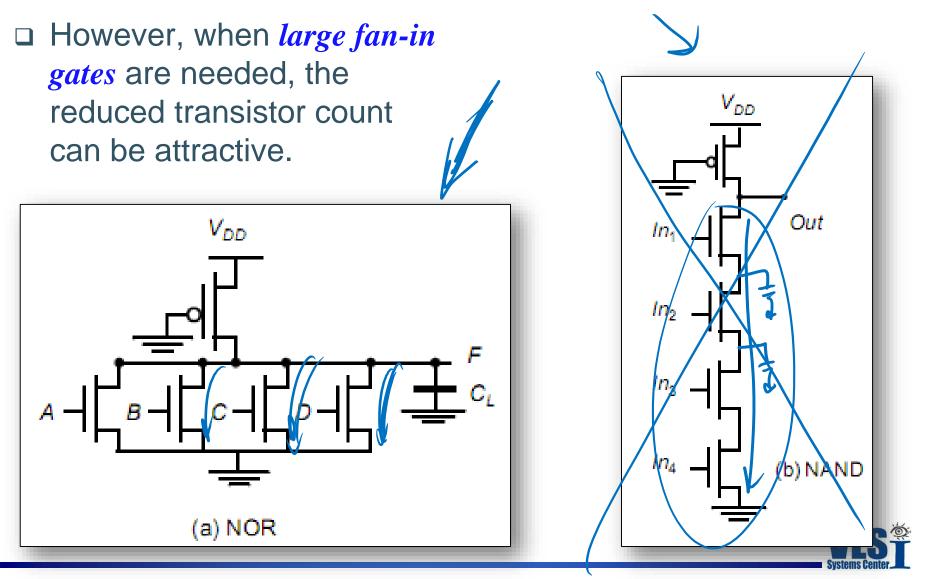

- □ The main drawback of *Standard CMOS* is its relatively large area (*2N transistors* to implement an *N-input gate*).

- In this lecture, we will start to overview a number of alternative logic families that try to reduce the number of transistors needed to implement a logic function.

#### What will we learn today?

3

**Digital Microelectronic Circuits**

#### 8.1 Ratioed Logic

8.2 Pseudo NMOS

8.3 LE of Pseudo NMOS

Let's start with an important concept that has driven a number of logic families:

# **RATIOED LOGIC**

**Digital Microelectronic Circuits**

- When we discussed Standard CMOS during the previous two lectures, we spent quite a while analyzing the sizes of the transistors.

- It is important to note that these sizing considerations improved the *performance* (=*speed*) of the logic gates, but not their *functionality*.

- In other words, even if we implemented the gates without size considerations, we would arrive at the requested logic function (though it might take a while...).

- Ratioed Logic is an attempt to reduce the number of transistors required to implement a given logic function, waiving the assurance of functionality.

- As its name implies, in order to ensure functionality, a certain *ratio of sizes* has to be kept between various devices that make up the gate.

- Ratioed Logic has another great disadvantage high static power dissipation – which makes it vary scarcely used. But the concept is implemented in quite a few complex circuits (such as memory circuits), and so it is important to understand.

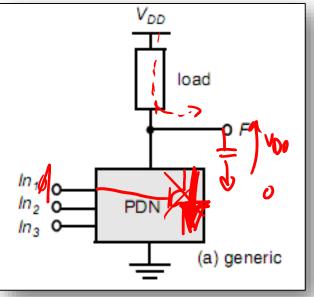

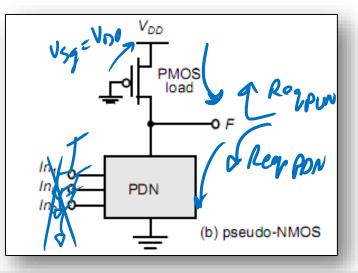

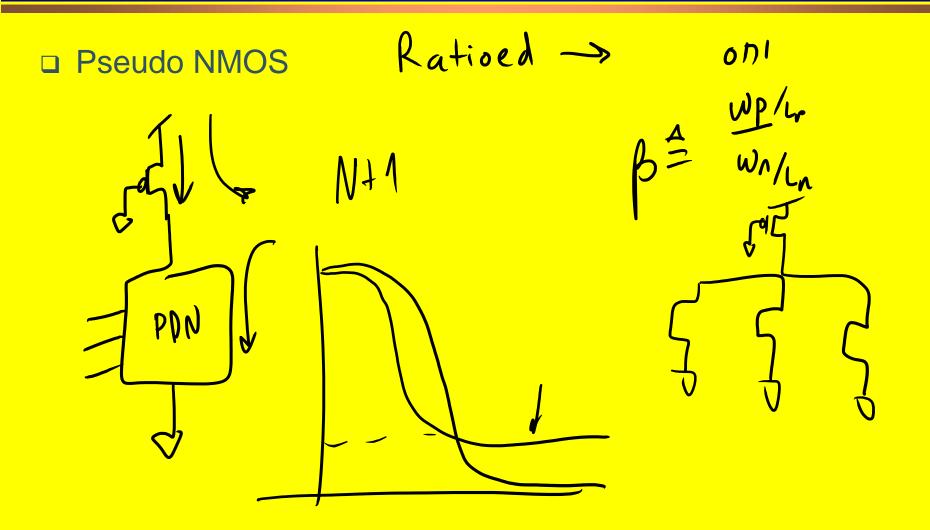

- □ The concept of *Ratioed Logic* uses the same *Pull Down Network* as *CMOS*, but uses a simple *Load* as its *Pull Up Network*.

- This Load constantly leaks current from the supply to the output capacitance. In this way, the output is charged when the PDN is closed, providing a '1'.

- On the other hand, the Load's resistance is much larger than that of an open PDN, so when the PDN is open, the output is pulled down to V<sub>OL</sub>.

- The ratio between the resistance of the Load and the PDN is crucial in designing such a gate, hence it is called "Ratioed" Logic.

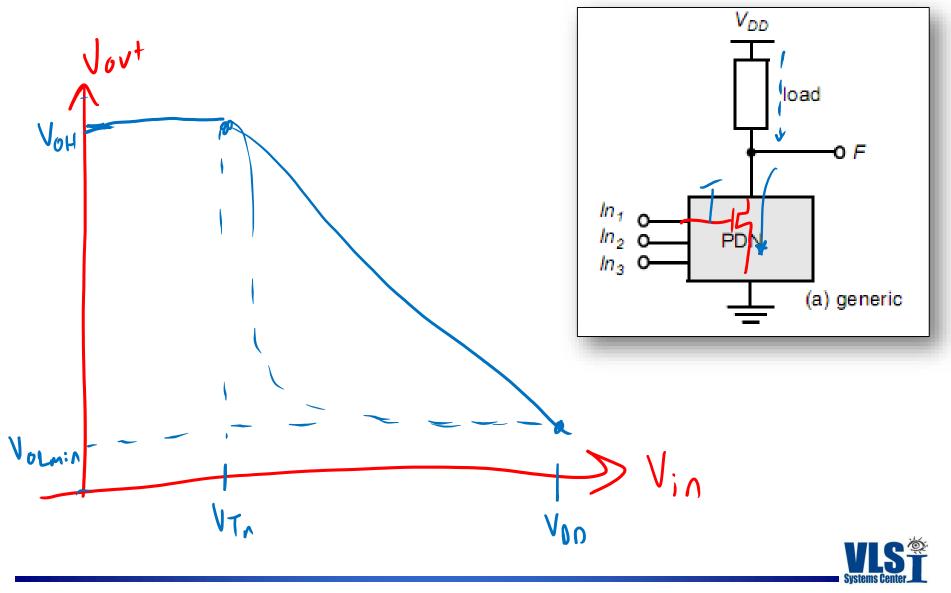

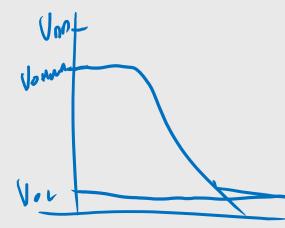

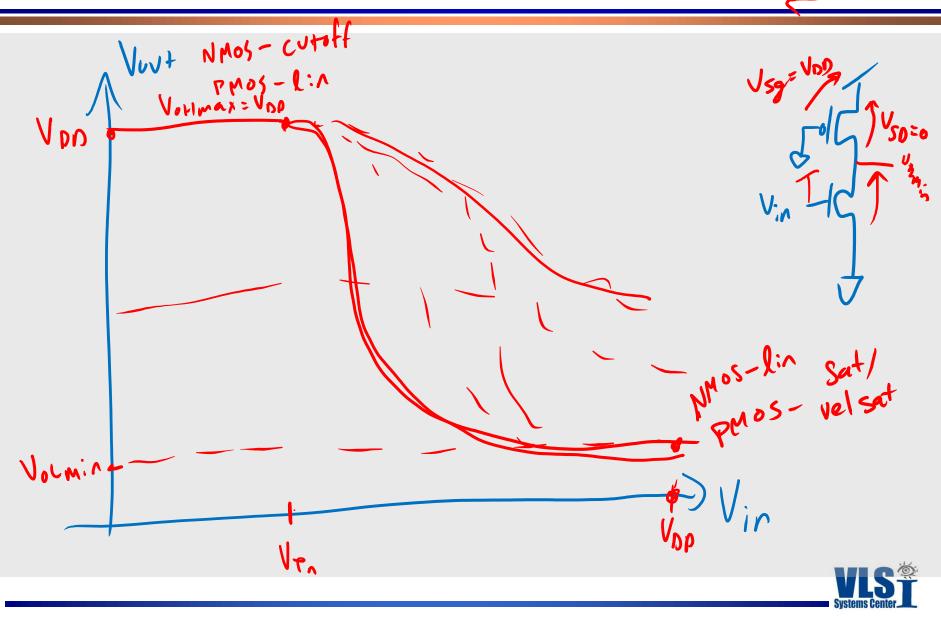

#### VTC of Generic Ratioed Logic Gate

#### **Ratioed Logic Characteristics**

N transistors + Load

$$V_{OH} = V_{DD}$$

$$V_{OL} = \frac{R_{PDN}}{R_{PDN} + R_L} \bigvee_{DD} 50$$

- Asymmetrical Response

- Static Power Consumption

- □ Slow pull up:  $t_{pLH} = 0.69C_{out}R_L$

# Load Implementation

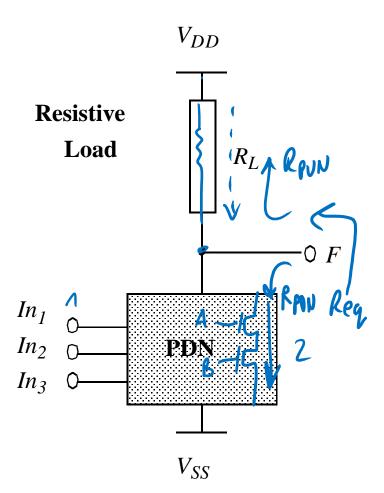

- Early Ratioed Logic designs used a simple resistor as the Load.

- This approach had several drawbacks, especially with the difficulty in *resistor implementation* in *VLSI*.

**Digital Microelectronic Circuits**

# Load Implementation

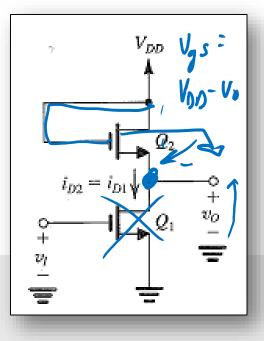

- Accordingly, the Load was replaced with a Diode-connected nMOS (V<sub>GD</sub>=0) a.k.a. Saturated Load Inverter.

- This circuit stopped conducting at

V<sub>GS</sub>=V<sub>DD</sub>-V<sub>Tn</sub> (weak '1') providing a largely reduced swing.

Voutmax = Voumax = VOD-K

# Load Implementation

- To improve the swing, the nMOS (also known as an "enhancement mode" nMOS) was replaced with a "Depletion Mode" nMOS

- □ This is a special, highly doped nMOS with a negative threshold voltage  $(V_{Tn} < 0)$ .

- This was used for some time until the *Pseudo nMOS inverter* was invented,

replacing the *nMOS load* with a *pMOS* connected to *ground*.

#### 8.1 Ratioed Logic

8.2 Pseudo NMOS

8.3 LE of Pseudo NMOS

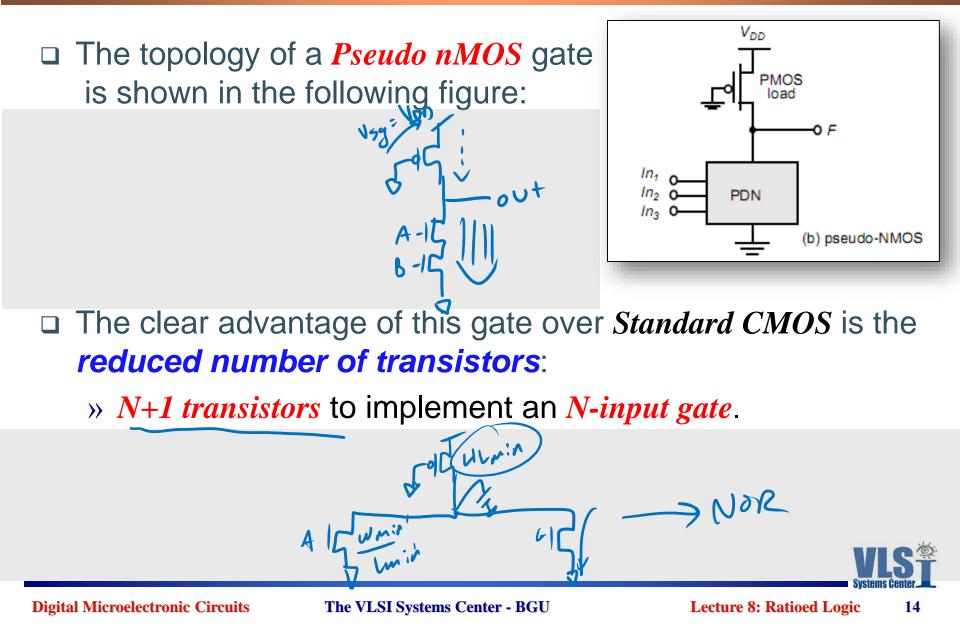

The only really surviving ratioed logic family is: **PSEUDO NMOS**

**Digital Microelectronic Circuits**

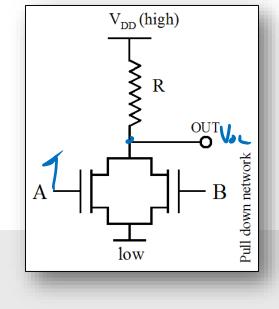

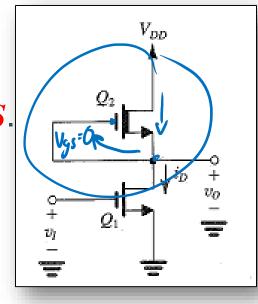

- □ Using a *pMOS* in the *PUN*, we get a *Strong* '1' when the *PDN* is closed, so  $V_{OHmax} = V_{DD}$ .

- On the other hand, when the *PDN* is open, there is a "*fight*" between the *PDN* and the *pMOS load*.

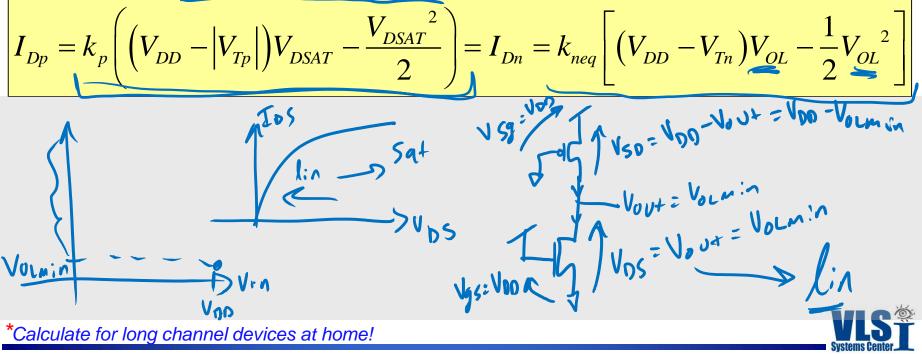

- To calculate V<sub>OLmin</sub>, we will equate the pMOS saturation current with the PDN current, assuming that it consists of nMOS devices in Linear Mode.

- □ We will mark the drive strength of the *PDN* as  $k_{neq}$  and assume *short channel devices*\*:

DSAT

$\mu_p \cdot W_p$

Making a few minor assumptions, we arrive at:

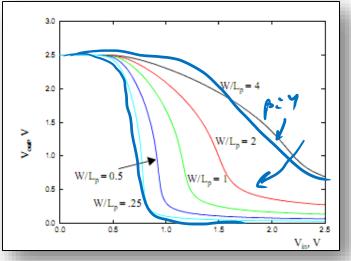

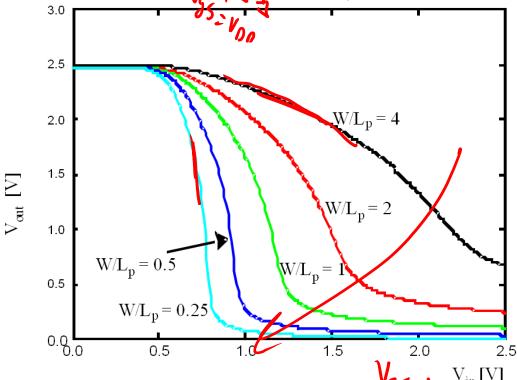

So to get a Low V<sub>OLmin</sub>, we need the pMOS to be much smaller than the equivalent width of the nMOS network.

Making the *pMOS* small means a *small charge current*, resulting in a large *t<sub>pLH</sub>*!

Figure 6.28 Voltage-transfer curves of the pseudo-NMOS inverter as a function of the PMOS size.

□ In addition, we get *static power dissipation* from the direct path between  $V_{DD}$  and GND when outputting a '0':

$$P_{low} = V_{DD}I_{low} \approx V_{DD}k_{p}\left(\left(V_{DD} - \left|V_{Tp}\right|\right)V_{DSAT} - \frac{V_{DSAT}^{2}}{2}\right)$$

$$V_{12} = V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V_{00}V$$

Accordingly, *Pseudo nMOS* won't usually be used in *low power* or *high frequency* applications.

**Digital Microelectronic Circuits**

#### **VTC of Pseudo NMOS**

## **Pseudo NMOS Characteristics Summary**

**\Box** Small  $\beta$  ratio (small pMOS, big PDN):

- » Lower VOL V

- » Better Gain

- » Less static power  $\checkmark$

- » Fast t<sub>pHL</sub>

- But...

- » Slow t<sub>pLH</sub>

- » Bigger capacitive load

#### □ In general:

- » N+1 Transistors

- » Only 1 NMOS load to previous stage

- » Make sure  $R_{PMOS}$  resistance at least 4 x  $R_{PDN}$

Now we can compare this logic family using our previously developed design methodology:

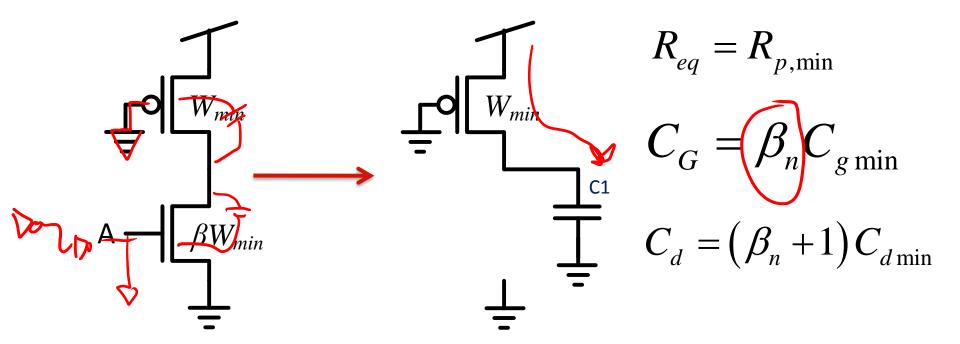

# **LOGICAL EFFORT OF PSEUDO NMOS**

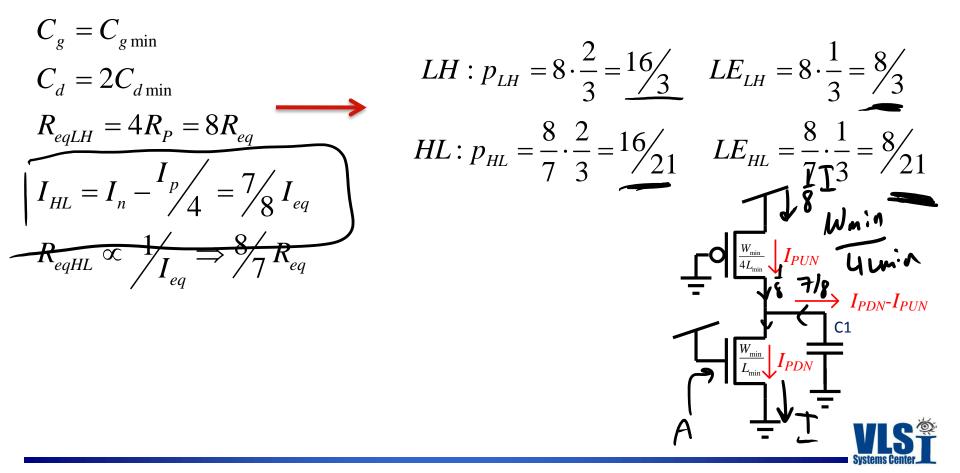

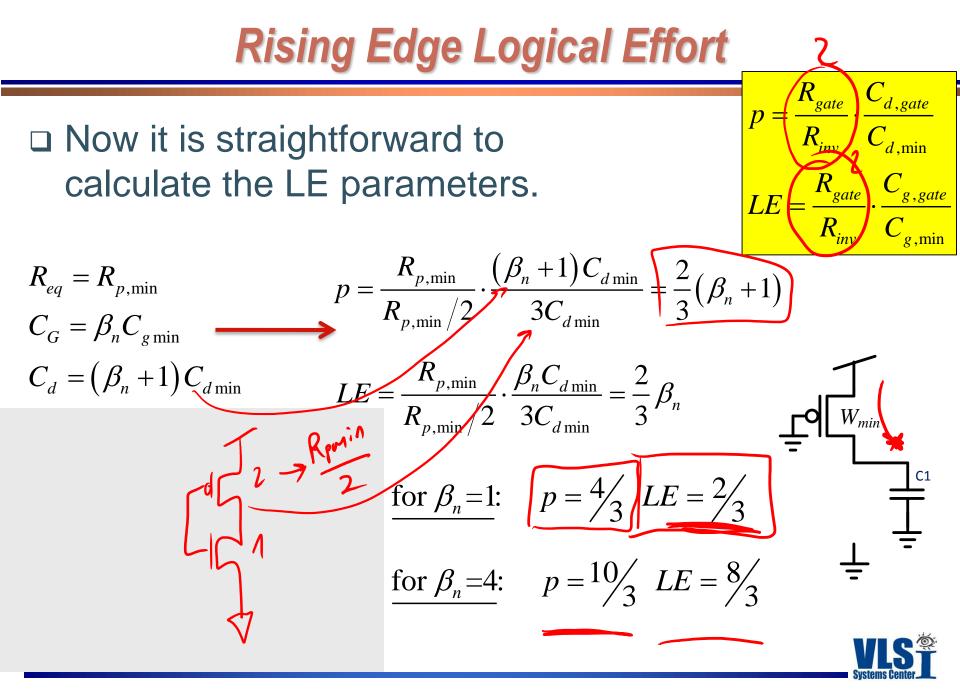

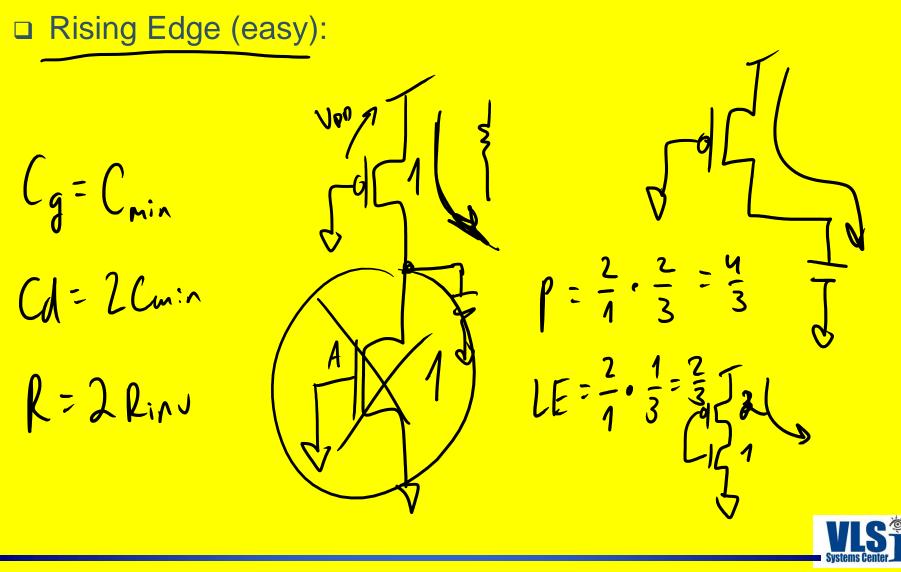

#### **Pseudo-NMOS – Rising Edge**

□  $t_{pLH}$  is simply through the pMOS:  $t_{pLH} = 0.69 \cdot C_L \cdot R_{p,min}$ □ Let's look at the Logical Effort parameters of this transition:

**Digital Microelectronic Circuits**

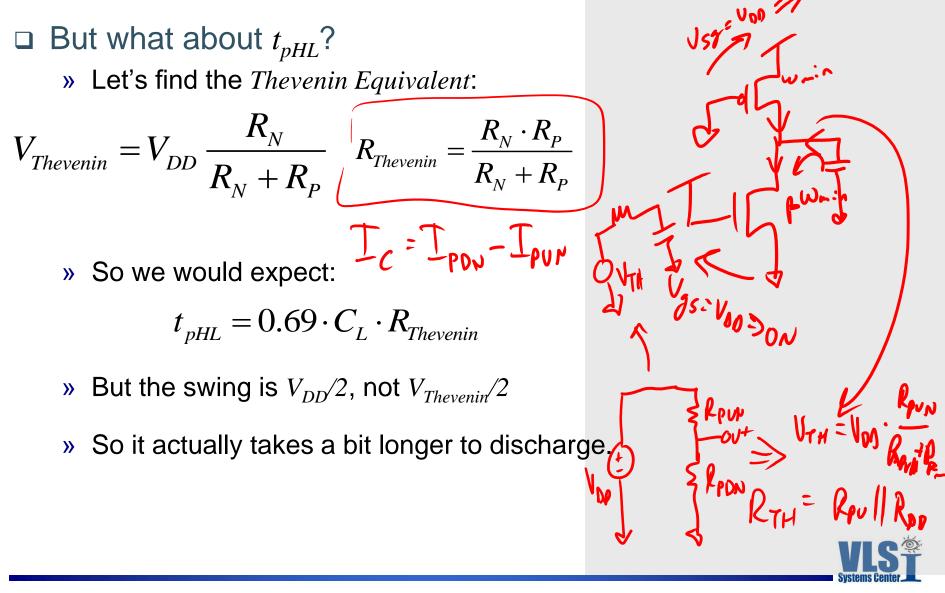

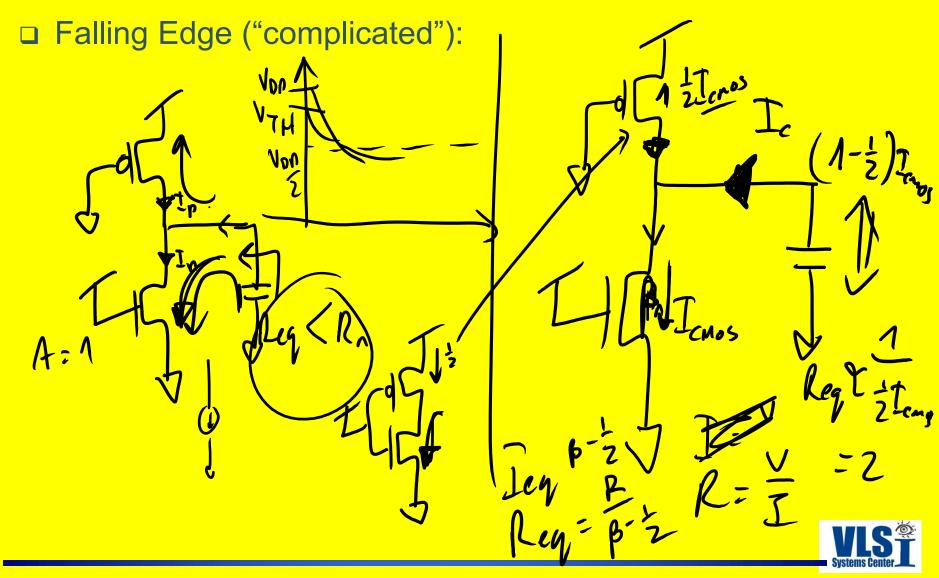

#### **Pseudo-NMOS – Falling Edge**

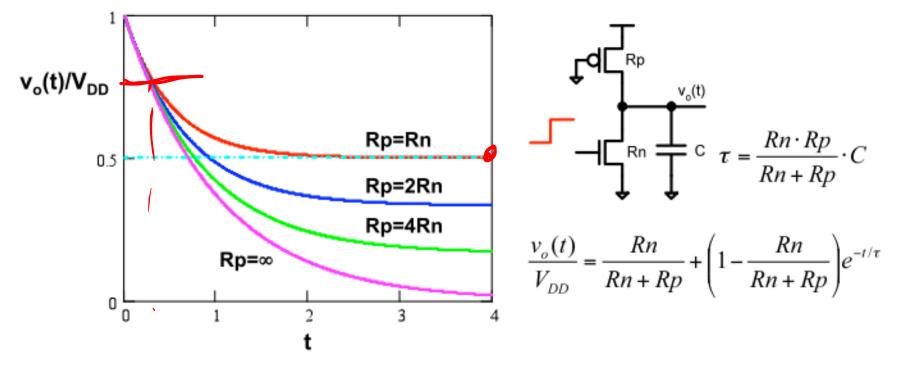

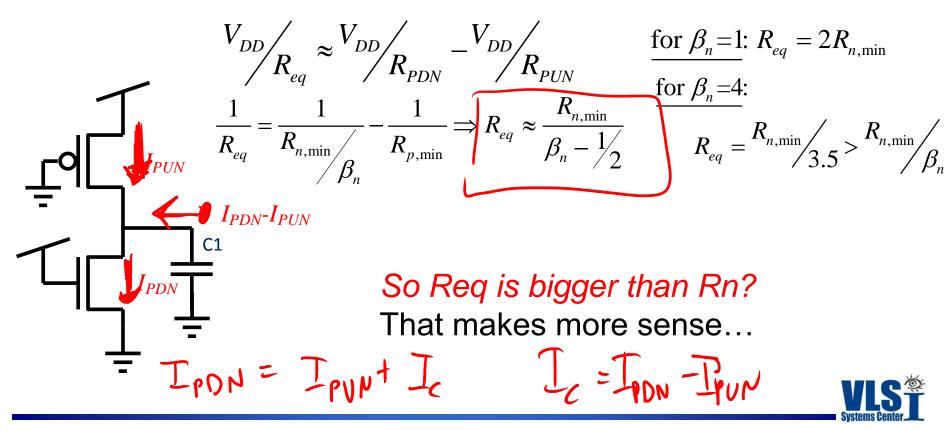

### **Response on Falling edge**

#### $\Box$ The smaller R<sub>PUN</sub>:

- » The smaller the swing, so it takes less time to reach  $0.5(V_{OH}-V_{OL})$

- » But the longer it takes to reach  $0.5V_{DD}$  !

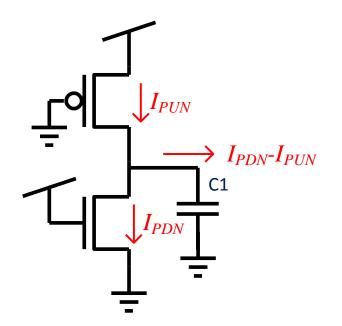

#### $\Box$ *t<sub>pHL</sub>* presents a new problem:

» Both the PUN and PDN are conducting.

$$R_{thevenin} = R_n \parallel R_p$$

So Req is smaller than Rn? How could this be – the pmos is "fighting" the discharge... It's because of the swing...

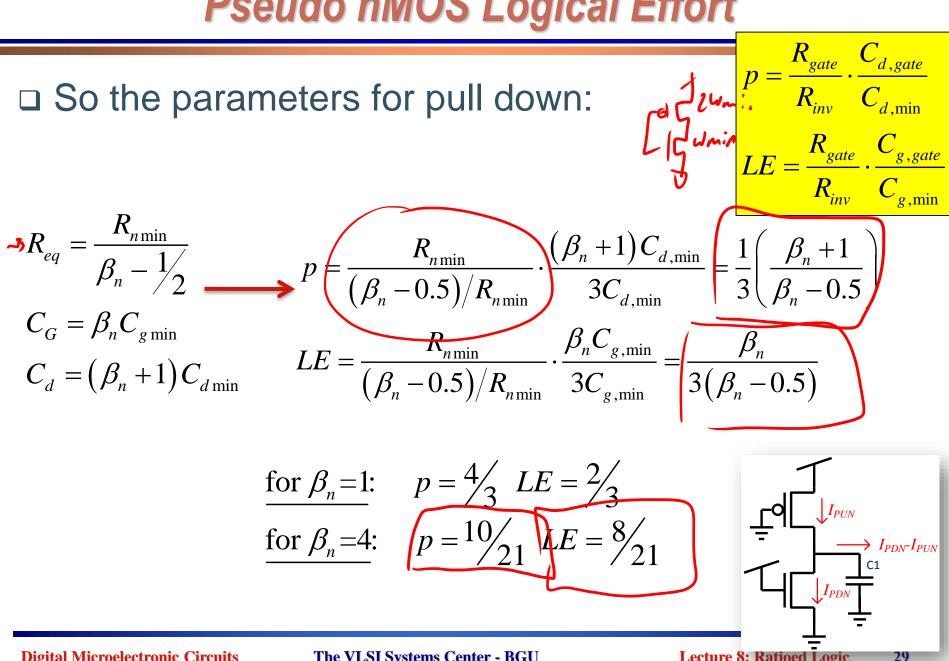

### **Pseudo nMOS Logical Effort**

#### □ What is the actual R?

- » Available Current is the difference between PDN and PUN.

- » The current is approximately proportional to the resistance.

#### Pseudo nMOS Logical Effort

**Digital Microelectronic Circuits**

The VLSI Systems Center - BGU

Lecture 8: Ratioed Logic

### **Pseudo nMOS Logical Effort - Summary**

□ So to summarize:

» With  $\beta=1$  (high V<sub>OL</sub>), we got:

$$t_{pLH}: p = \frac{4}{3} \quad LE = \frac{2}{3} \quad t_{pHL}: p = \frac{4}{3} \quad LE = \frac{2}{3}$$

- » Our LE is *LOWER* than an inverter!

- » But don't forget we have depleted noise margins and we have static power...

- » With  $\beta = 4$  (more realistic), we got:  $t_{pLH} : p = \frac{10}{3} LE = \frac{8}{3}$   $t_{pHL} : p = \frac{10}{21} LE = \frac{8}{21}$

- » Our HL transition has much better performance than CMOS!

- » But the LH transition is much worse.

**Last Lecture**

#### **Last Lecture**

#### **Last Lecture**

**Digital Microelectronic Circuits**

**Another Example**

□ What if we were to give the pMOS a long L?

» Say we want  $\beta = 4$ , so we would choose  $W_p/L_p = W_{min}/4_{Lmin}$