# Digital Microelectronic Circuits (361-1-3021)

Presented by: Adam Teman

Lecture 4: The CMOS Inverter

1

**Digital Microelectronic Circuits**

#### **Last Lectures**

#### Moore's Law

#### □ Terminology

- » Static Properties

- » Dynamic Properties

- » Power

#### □ The MOSFET Transistor

- » Shockley Model

- » Channel Length Modulation, Velocity Saturation, Body Effect

2

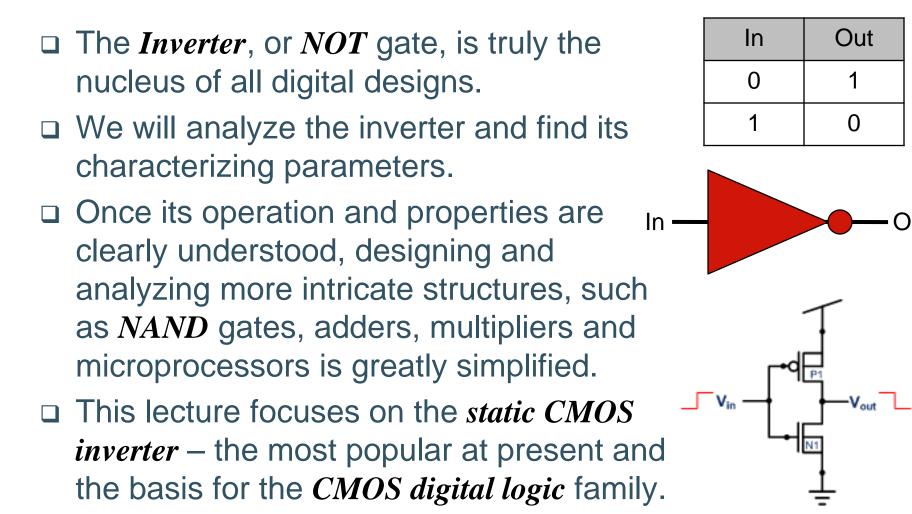

## **This Week - Motivation**

#### What will we learn today?

As usual, we'll start with

# **AN INTUITIVE EXPLANATION**

5

- A Static CMOS Inverter is modeled on the double switch model.

- The basic assumption is that the switches are Complementary, i.e. when one is on, the other is off.

- When the top switch is on, the supply voltage propagates to the output node.

- □ When the *bottom switch* is *on*, the *ground voltage* is propagated out.

V

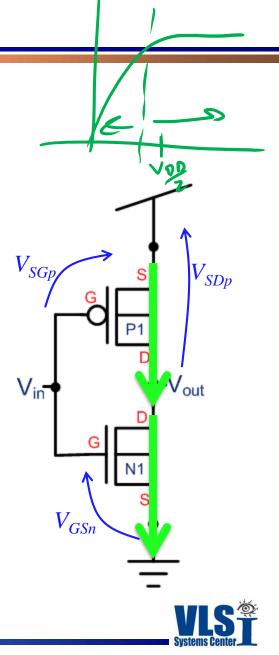

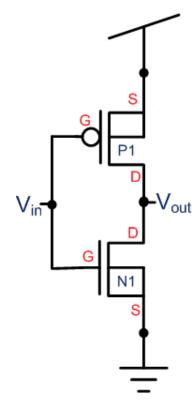

- Now we will replace the model switches V with real voltage controlled switches – MOS Transistors.

- We will use complementary transistors

one *nMOS* and one *pMOS*, and hook

them up to the *same input voltage*.

- Now, when we set a high input voltage, the nMOS is on and the pMOS off. The ground voltage propagates.

- When we put a low input voltage, the pMOS is on and the nMOS is off. The supply voltage propagates.

- □ We've built an *inverter*!

- □ We mark the connection to  $V_{DD}$  with a horizontal or slanted bar.

- □ Accordingly,  $V_{DD}$  represents a logical '1' and GND represents a logical '0'.

- □ Inputting  $V_{DD}$  to the CMOS inverter will present *GND* at the output. Inputting *GND* will present  $V_{DD}$  at the output.

- This characteristic is non-trivial and is one of the advantages of CMOS design. It is known as "Rail to Rail Swing".\*\*

\* It can also be called V<sub>CC</sub>, regarding the Collector of BJT transistors.

\*\* "*Rails*" are the supply voltages, i.e.  $V_{DD}$  and *GND*. If a voltage is connected to the nMOS Source instead of *GND*, we refer to this voltage as  $V_{SS}$ .

8

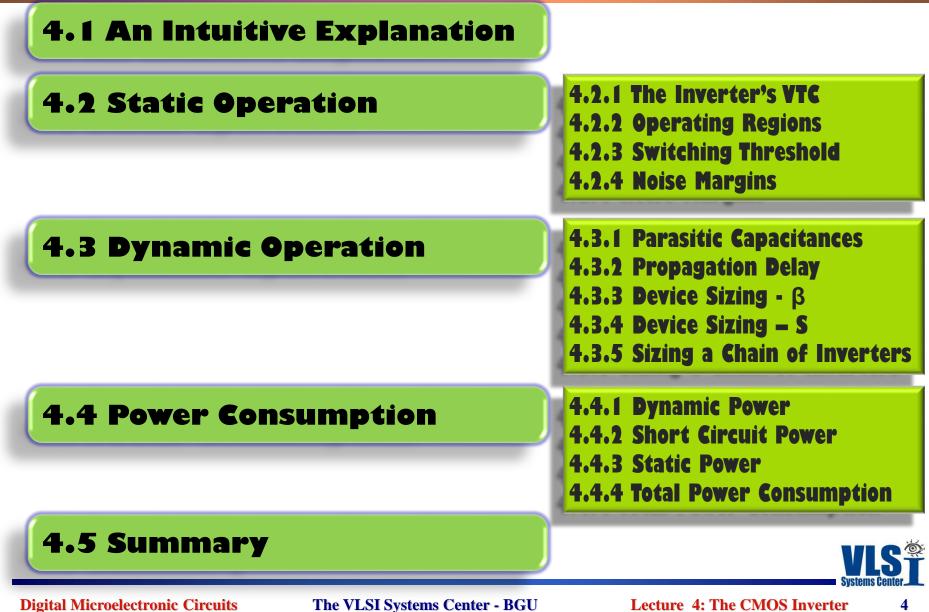

#### 4.1 An Intuitive Explanation

#### 4.2 Static Operation

4.3 Dynamic Operation

**4.4 Power Consumption**

4.5 Summary

Now that we understand the principles, we'll analyze

# **STATIC OPERATION**

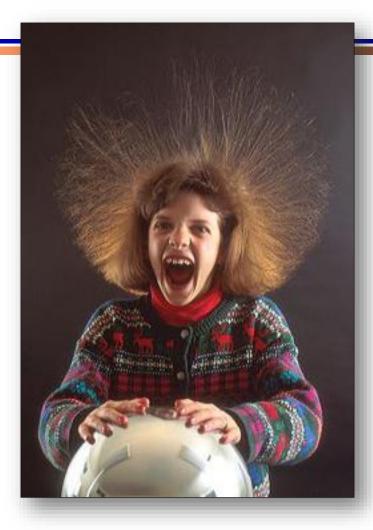

## **Reminder: The Unified MOSFET Model**

**Digital Microelectronic Circuits**

#### **Reminder: Static Properties**

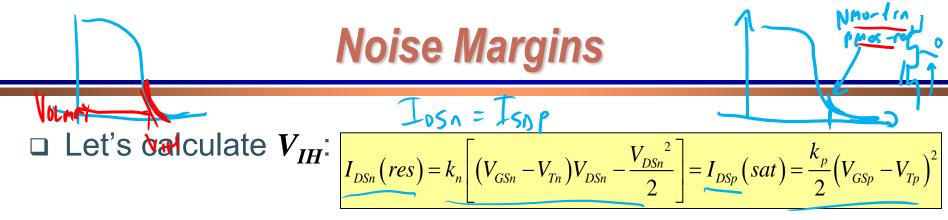

# VTCNoise Margins

**Digital Microelectronic Circuits**

□ We can see that:

i۵

$$I_{SDp} = I_{DSn}$$

Vot

$$V_{GSn} = V_{in}$$

$$V_{DSn} = V_{out}$$

$$V_{SGp} = V_{DD} - V_{in}$$

The Inverter's VTC

$$V_{SDp} = V_{DD} - V_{out}$$

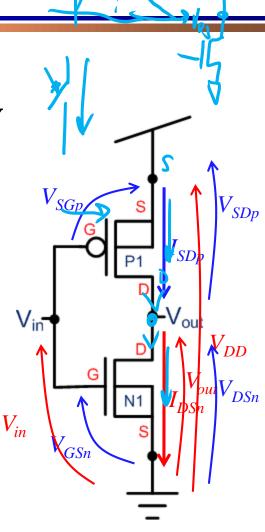

#### The Inverter's VTC

Since V<sub>in</sub> and V<sub>out</sub> are the input and output voltages of the nMOS transistor, we will change the coordinates of the pMOS.

#### The Inverter's VTC

Nosvinter seidtion of imprestenting if and places the object of the places of the p

14

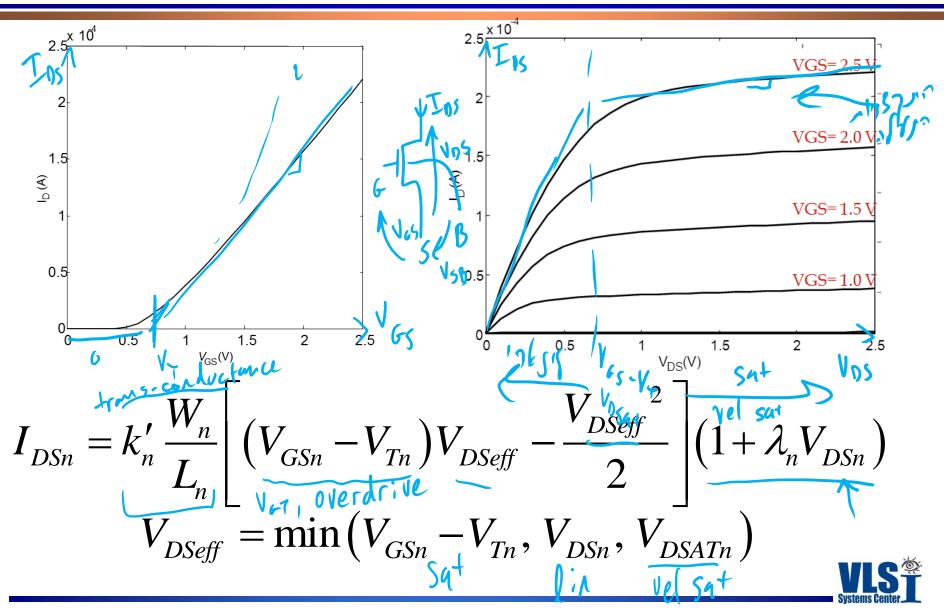

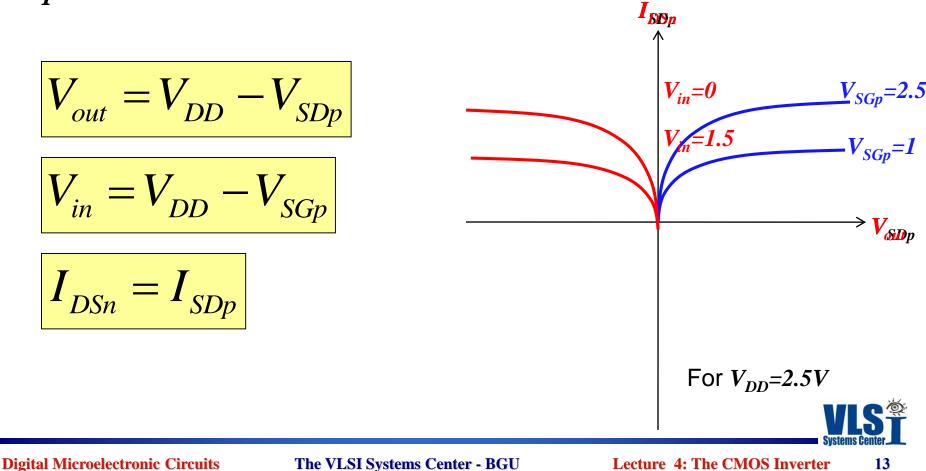

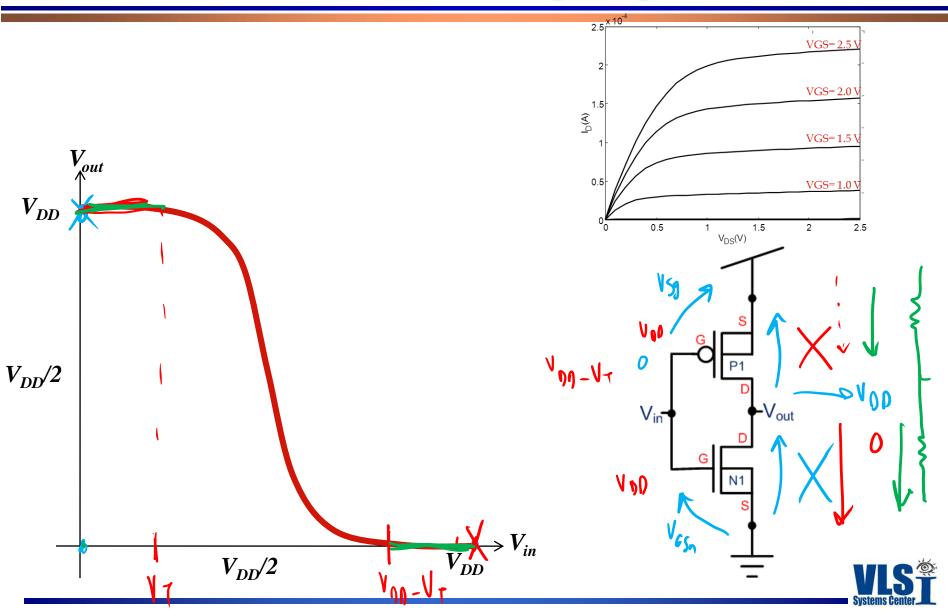

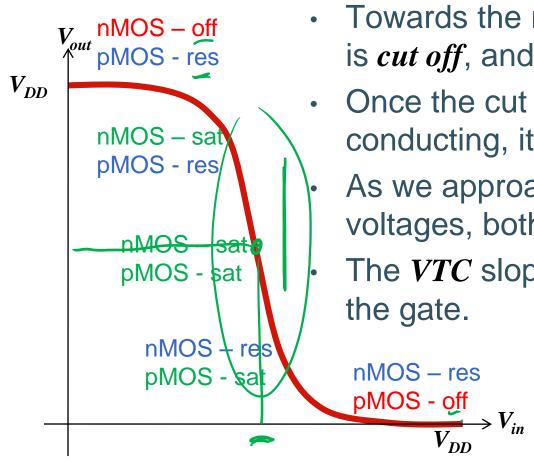

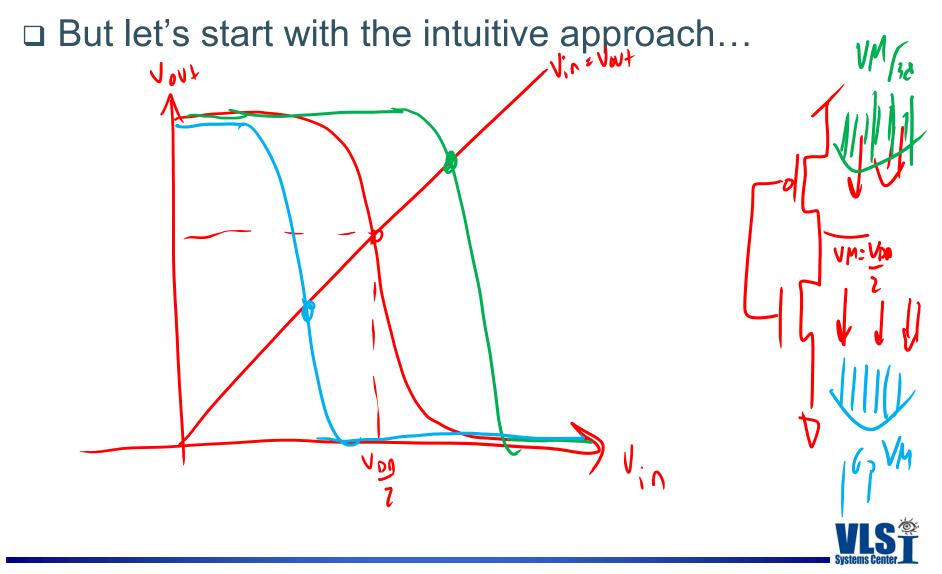

Putting all the intersection points on a graph with the corresponding output voltage will give us the CMOS inverter's VTC:

## **Intuitive Operating Regions**

**Digital Microelectronic Circuits**

#### **Operating Regions** Tin Let's figure out what region of operation each transistor is in throughout the VTC curve.\* \* Considering Long Channel Transistors With $V_T < V_{DD}/2$ K NHOSAFY I:r Vout $V_{in} < V_T$ V<sub>DD</sub> V<sub>out</sub> V<sub>SGp</sub> $V_{SDp}$ -0 $|V_{GSn} = V_{in} < V_T \rightarrow Cutoff$ $V_{SGp} = V_{DD} - V_{in} > V_T$ $V_{SDp} = V_{DD} - V_{out} < V_{SGp} - V_T$ V<sub>in</sub>-→ Linear $V_{DD}/2$ V<sub>in</sub> $\overline{V_{DD}}$ *V<sub>DD</sub>*/2 $V_{T}$

**Digital Microelectronic Circuits**

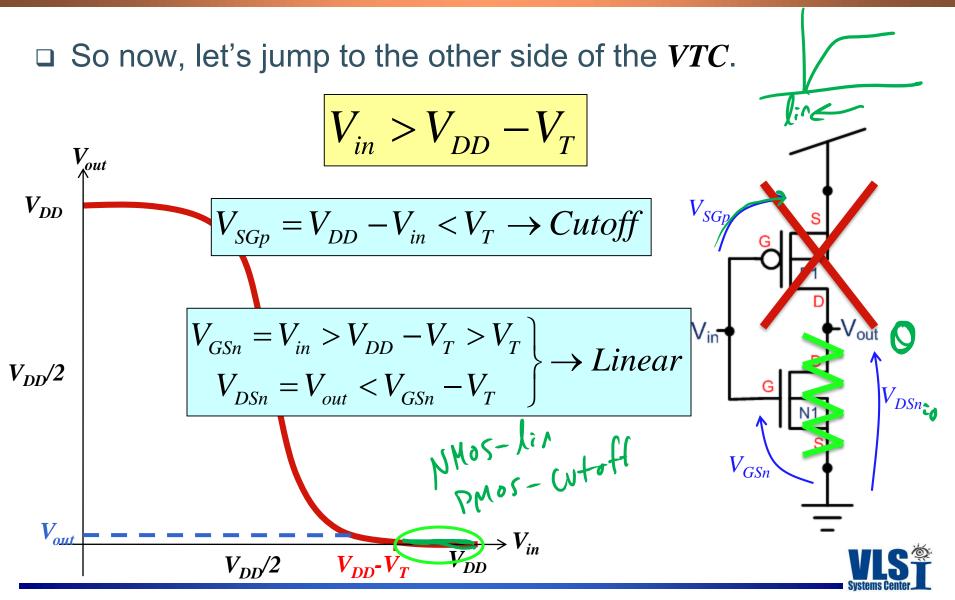

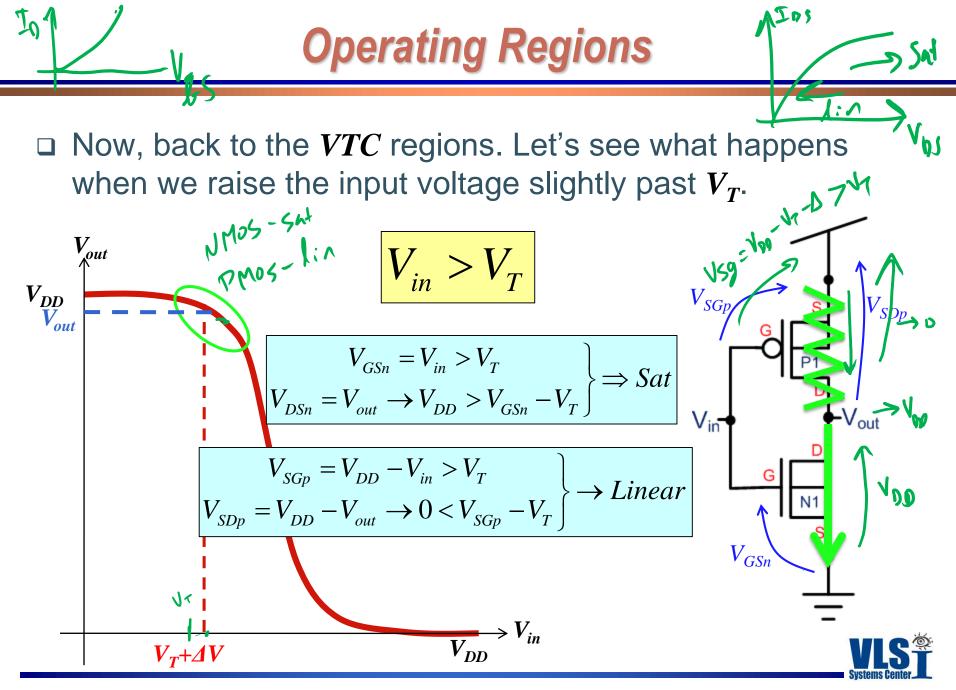

## **Operating Regions**

**Digital Microelectronic Circuits**

**Digital Microelectronic Circuits**

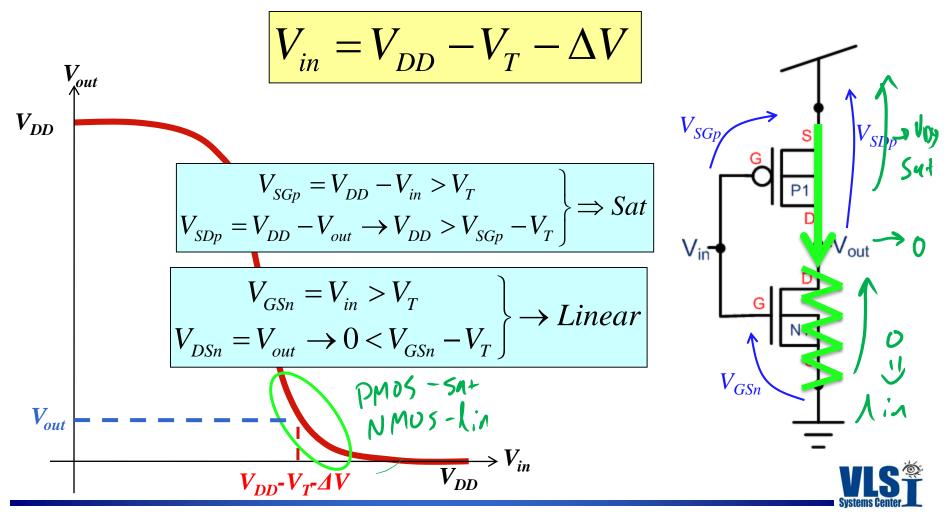

## **Operating Regions**

$\Box$  The same when  $V_{in}$  is a bit more than  $V_T$  lower than  $V_{DD}$ .

**Digital Microelectronic Circuits**

## **Operating Regions**

□ Finally, we have the middle area, where:

$$V_{in} = V_{DD} / 2 \pm \Delta V$$

$$V_{DD} = V_{SGp} = V_{DD} - V_{in} \approx V_{DD} / 2 > V_{T}$$

$$V_{SDp} = V_{DD} - V_{out} \approx V_{DD} / 2 > V_{SGp} - V_{T}$$

*V<sub>DD</sub>*/2

$$V_{GSn} = V_{in} \approx V_{DD}/2 > V_T$$

$$V_{DSn} = V_{out} \approx V_{DD}/2 > V_{GSn} - V_T$$

$$V_{DSn} = V_{out} \approx V_{DD}/2 > V_{GSn} - V_T$$

**Digital Microelectronic Circuits**

$V_{out}$

**V**<sub>out</sub>

The VLSI Systems Center - BGU

$V_{DD}$

V<sub>in</sub>

#### □ To Sum it up:

- Towards the rails, one of the transistors is *cut off*, and the other is *resistive*.

- Once the cut off transistor starts conducting, it immediately is *saturated*.

- As we approach the middle input voltages, both transistors are *saturated*.

- The *VTC* slope is known as the *Gain* of the gate.

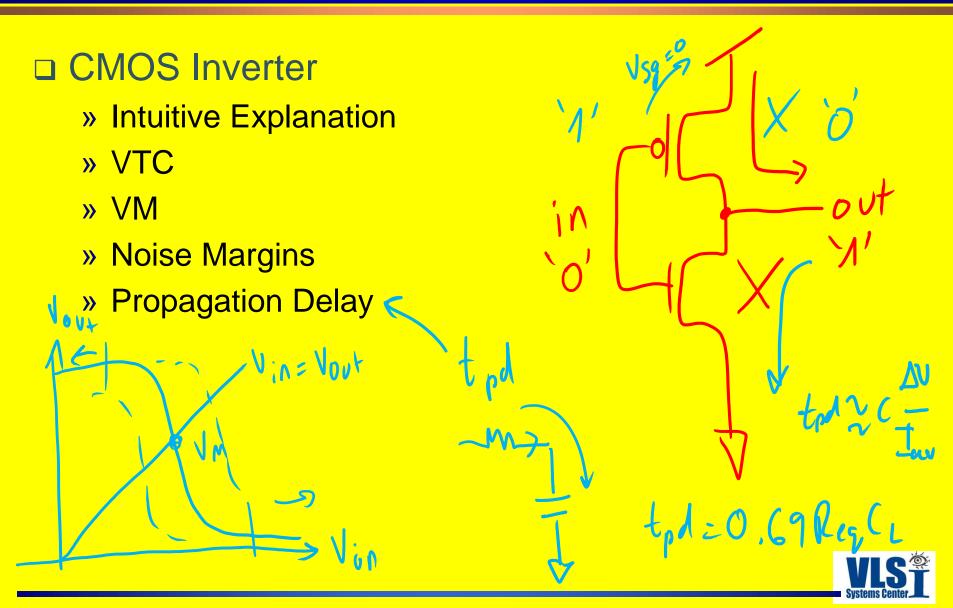

## **Switching Threshold**

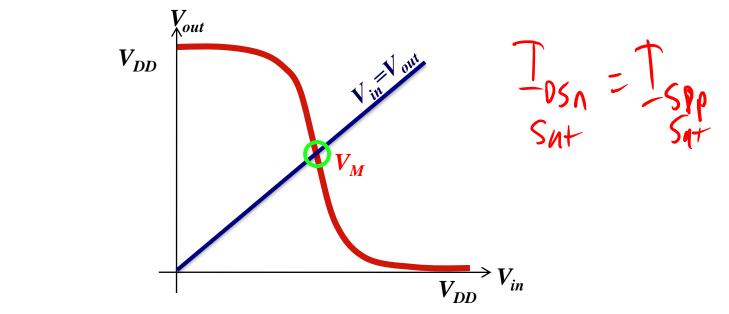

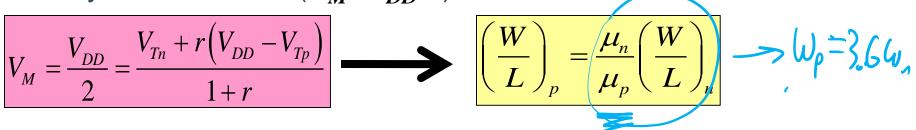

□ The *Switching Threshold*,  $V_M$ , is the point where  $V_{in} = V_{out}$ . □ This can be calculated:

» Graphically, at the intersection of the VTC with  $V_{in}=V_{out}$

» Or analytically, by equating the *nMOS* and *pMOS* saturation currents with  $V_{in} = V_{out}$ .

#### **Switching Threshold**

$\Box$  Let's analytically compute  $V_M$ .

» Remember, the saturation current for a MOSFET is given by:

Switching Threshold

$$I_{DS} = \frac{k}{2} (V_{GS} - V_T)^2 (1 + 2V_{DS})$$

» Lets assume  $\lambda = 0$  and we'll equate the two currents:

$$I_{D} = \frac{k_{n}}{2} (V_{GSn} - V_{Tn})^{2} = \frac{k_{p}}{2} (V_{SGp} - V_{Tp})^{2}$$

» Now we'll substitute:

$$V_{GSn} = V_{in} = V_M$$

$$V_{SGp} = V_{DD} - V_{in} = V_{DD} - V_M$$

» And we'll arrive at:

$$V_{M} = \frac{V_{Tn} + r(V_{DD} - V_{Tp})}{1 + r}$$

$$r \triangleq \sqrt{\frac{k_{p}}{k_{n}}}$$

**Digital Microelectronic Circuits**

The VLSI Systems Center - BGU

KE

+ DSn(SA+) = Tso, (sa+)

Vno-N.

$V_{in}$

- □ As we can see, *r* is an important factor in setting the *switching threshold*.

- *r* is a design parameter, that is set by the *drive strength ratios* of the *nMOS* and *pMOS*:

$$r_{long\_channel} \triangleq \sqrt{\frac{k_p}{k_n}}$$

$k \triangleq k' \frac{W}{L} = \mu C_{ox} \frac{W}{L}$

□ Using the current equations again, we can find the *drive strength ratio* for a desired  $V_M$ :

$$\frac{k_p}{k_n} = \left(\frac{V_M - V_{Tn}}{V_{DD} - V_M - V_{Tp}}\right)^2$$

**Digital Microelectronic Circuits**

## **Switching Threshold**

□ A symmetric VTC ( $V_M = V_{DD}/2$ ) is often desired. In this case:

□ Generally, the same length  $(L_{min})$  is taken for all transistors in digital circuits, and so for a symmetric *VTC*:

27

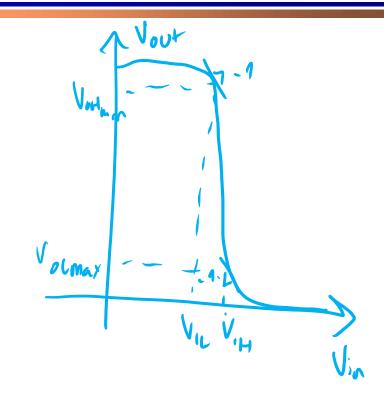

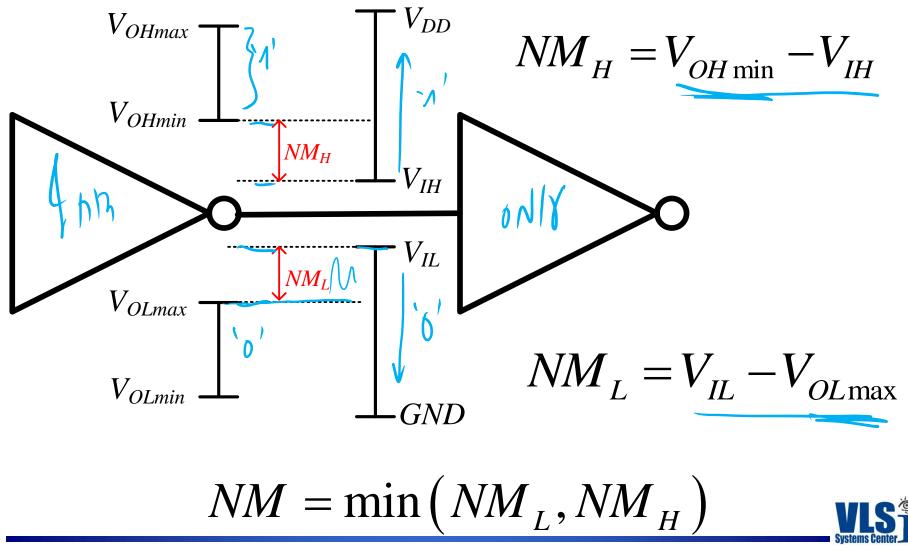

#### **Reminder: Noise Margins**

**Digital Microelectronic Circuits**

□ One of the CMOS logic family's advantages is a *Full Rail to Rail Swing*. In other words: V = -V

$$V_{OH \max} = V_{DD}$$

$V_{OL \min} = GND$

□ To calculate the *Noise Margins*, we will need to find  $V_{IL}$  and  $V_{IH}$ . These are the points where the *gain* is -1.

$V_{DD}$

- To do this we will equate the currents:

- »  $V_{IL}$   $\rightarrow$  nMOS *sat*, pMOS *res*

- »  $V_{IH} \rightarrow$  nMOS *res*, pMOS *sat*

$V_{DD}$

□ Assuming matching devices  $(k_n = k_p, V_{T_n} = V_{T_p})$ :

$$\left(V_{IN} - V_{T}\right)V_{out} - \frac{V_{out}^{2}}{2} = \frac{1}{2}\left(V_{DD} - V_{IN} - V_{T}\right)^{2}$$

Differentiating and equating -1, we reach:

$$V_{IH} = \frac{1}{8} \left( 5V_{DD} - 2V_T \right)$$

$\Box$  Doing the same for  $V_{IL}$  or using symmetry, we reach:

$$V_{IL} = \frac{1}{8} \left( 3V_{DD} + 2V_T \right)$$

□ Accordingly, for a matched *long-channel* device, and assuming  $V_{OHmin} \rightarrow V_{OHmax}$  and  $V_{OLmax} \rightarrow V_{OLmin}$  in *CMOS*, we get:

$$NM_{H} = NM_{L} \approx V_{DD} - V_{IH} = V_{IL} - 0 = \frac{1}{8} (3V_{DD} + 2V_{T})$$

**Digital Microelectronic Circuits**

The previous analysis "assumed" many things and therefore SHOULD NOT be memorized.

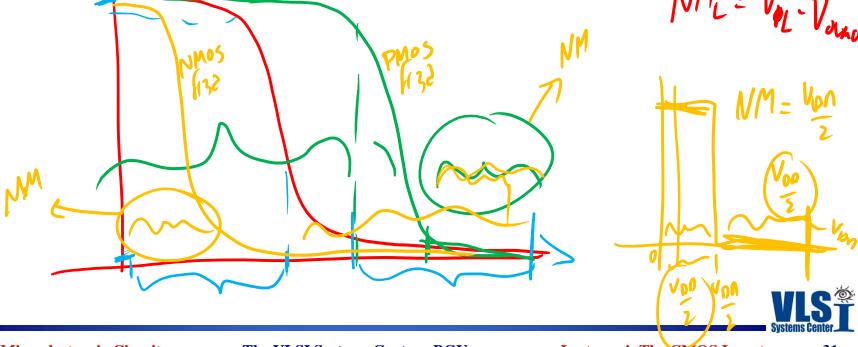

□ Let us look at the noise margins intuitively to try and understand trade offs:  $MM = V_0$

#### **Summary of Static Properties**

- When Vin<VT or Vin>VDD-VT, one of the networks (PUN/PDN) is off, providing Rail to Rail Swing.

- □ The skew of the VTC is set by the sizing ratio between the PUN and PDN.

- Analytic Noise Margin calculation is rigorous and approximation should be used when possible.

4.1 An Intuitive Explanation

4.2 Static Operation

4.3 Dynamic Operation

**4.4 Power Consumption**

4.5 Summary

Now that we see how the inverter behaves in steady state, we will analyze it's transient:

## **DYNAMIC OPERATION**

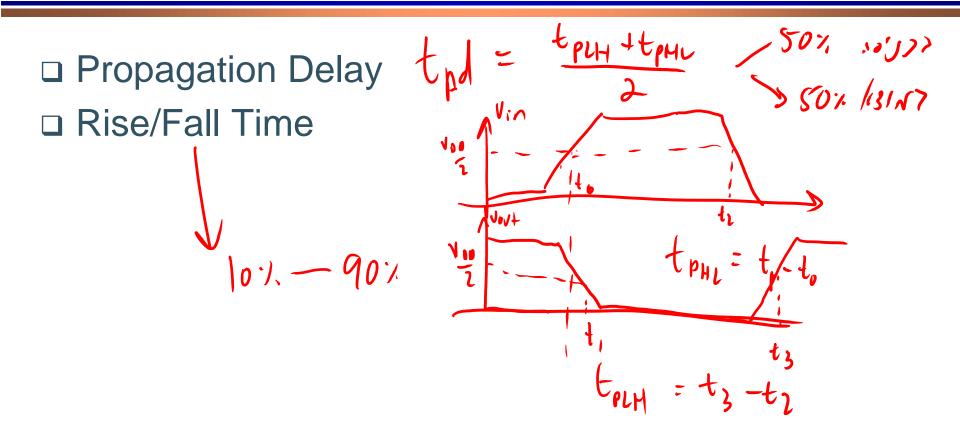

#### **Reminder: Dynamic Properties**

**Digital Microelectronic Circuits**

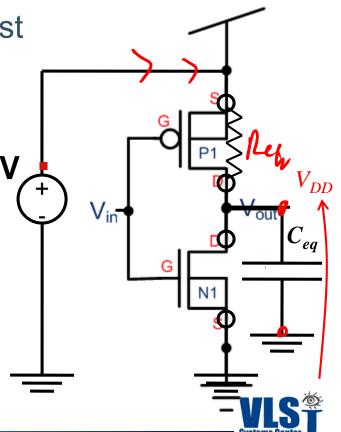

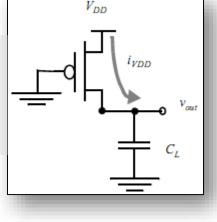

- Remember that our transistors have *capacitance* connected to the *output node*.

- We'll calculate the capacitance values in the next lecture, but for now, let's just use and *equivalent output capacitance*.

- When the input is low our *pMOS* is a non-linear *resistor* and our *nMOS* is *cut off*, so we get a *simple RC circuit*.

- □ Our capacitance is *charged*, bringing the output voltage to  $V_{DD}$ .

INMP

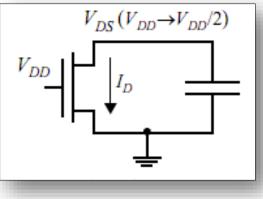

- When the input is high, we essentially have closed the top switch and opened the bottom one.

- □ This creates a *resistive path* from the capacitor to *GND*, and blocks the path from the supply to the output.

- □ Again we have an *RC network*, though this time we are just *discharging* the capacitance to *GND*.

□ We end up with an output equal to *GND*.

Vin

- So we saw that, a switching CMOS inverter charges and discharges a parasitic output capacitance.

- □ During the switching process, we can create a model that will transform the circuit into a *simple RC network*.

- In this way, we can easily derive a first order analysis of the CMOS dynamic operation for *propagation delay* and *power consumption* calculation.

□ For now, let us make the following assumptions:

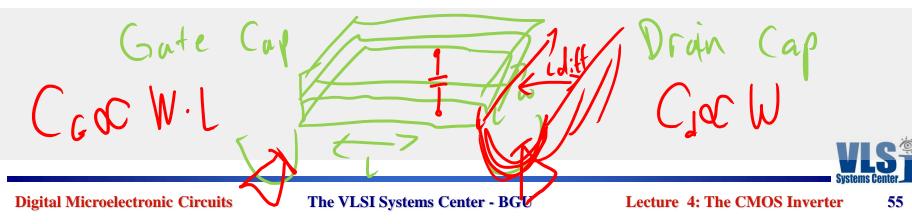

- » A transistor has a gate capacitance that is proportional to its area (W\*L)

- » A transistor has a diffusion capacitance that is proportional to its width (W)

b

( (∢ ♥

For now we will use a very simple model to represent all the parasitic capacitances between the output node and ground.

## **Propagation Delay**

□ Using our simple model for *load capacitance*, we can write:

- We will look at three ways to calculate the propagation delay:

- » By solving the integral above.

- By approximating the average current

- » By using equivalent resistance

□ At this point  $V_{DSn} = V_{DD} > V_{GS} - V_T$ , so N1 is in *saturation* and the discharge current is given by:

$$I_{DSn} = \frac{k_n}{2} \left( V_{In} - V_T \right)^2 \left( 1 + \lambda V_{out} \right)$$

• Assuming  $\lambda = 0$  and integrating until N1 enters the linear region:  $V_{out}$   $v_{DD}$   $v_{DD}$   $v_{DD}$   $v_{DD}$   $v_{DD}/2$   $t_{p1}$  $t_{p1} = \int_{v_{DD}}^{v_{DD}-v_T} \frac{C_{load}}{i_D(sat)} dv = \frac{C[V_{DD} - (V_{DD} - V_T)]}{\frac{k_n}{2}(V_{DD} - V_T)^2}$

**Digital Microelectronic Circuits**

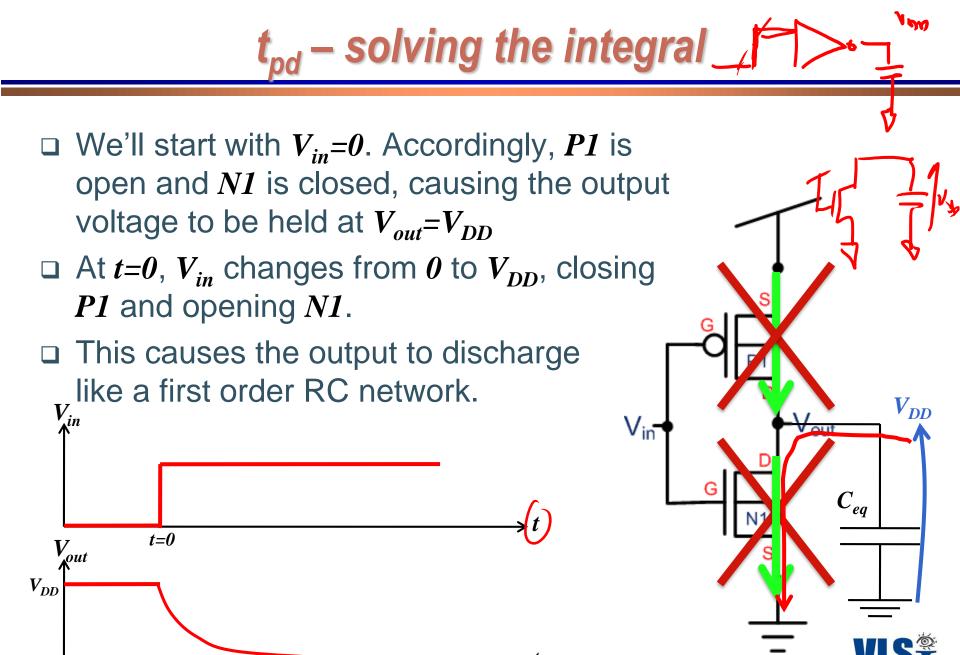

## t<sub>pd</sub> – solving the integral

□ Now  $V_{DSn} < V_{GS}$ - $V_T$  and so N1 goes into *linear* operation with:

$$I_{DSn}(res) = k_n \left[ \left( V_{in} - V_T \right) V_{out} - \frac{V_{out}^2}{2} \right]$$

□ We'll write an expression for the change in voltage:

$$dV_{out} = -\frac{i_{DSn}}{C_{load}} dt = -\frac{k_n}{C_{load}} \left[ (V_{in} - V_T) V_{out} - \frac{V_{out}^2}{2} \right]$$

And arrive at the following integral:

$$t_{p2} = \int_{t_1}^{t_{pHL}} dt = \frac{C_{load}}{k_n (V_{DD} - V_T)} \int_{V_{DD} - V_T}^{V_{DD}/2} \frac{dV_{out}}{\frac{1}{2(V_{DD} - V_T)}} V_{out}^2 - V_{out}$$

**Digital Microelectronic Circuits**

## t<sub>pd</sub> – solving the integral

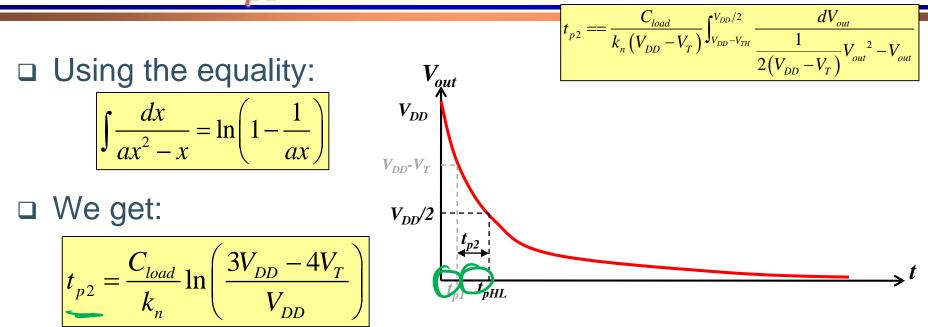

□ And putting together the two parts, we get:

- Instead of solving the integral, we can sometimes assume a linear change in current to make life much easier.

- □ This assumption just lets us find the average current between t=0 and  $t=t_{pHL}$  and calculate:

## t<sub>pd</sub> – average current

**Digital Microelectronic Circuits**

## t<sub>pd</sub> – average current

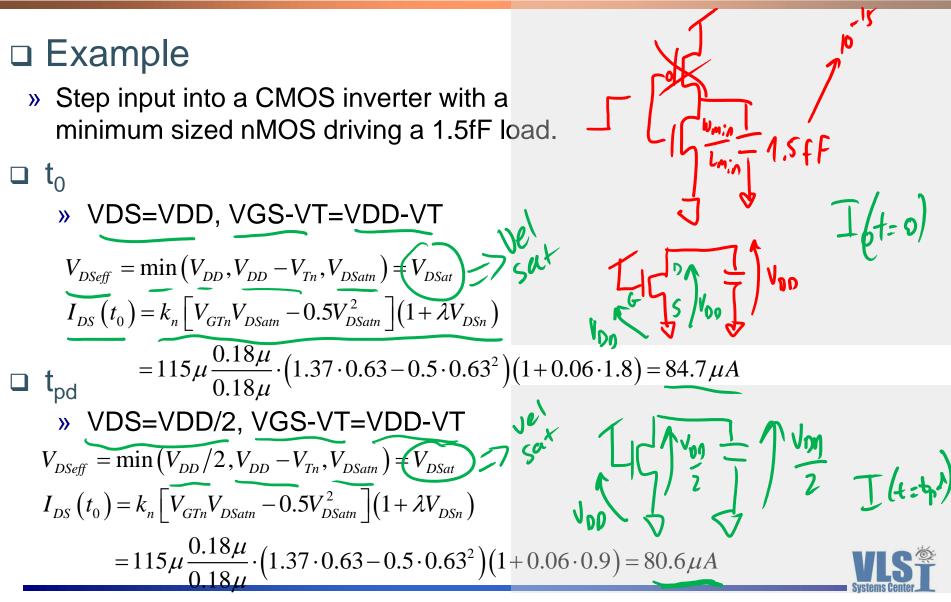

» The average current is:

$$I_{Avg} = 0.5 \left( I_{DS} \left( t_0 \right) + I_{DS} \left( t_{pd} \right) \right) = \frac{84.7 \,\mu + 80.6 \,\mu}{2} = 82.65 \,\mu A$$

» So we can find the delay:

$$t_{pd} = C_L \frac{V(t_0) - V(t_{pd})}{I_{Avg}} = 1.5f \frac{0.9}{82.65\mu} = 16.33 ps$$

$$I_{l} = C_L \frac{V(t_0) - V(t_{pd})}{I_{Avg}} = 1.5f \frac{0.9}{82.65\mu} = 16.33 ps$$

$$I_{l} = C_L \frac{V_l}{J_{l}}$$

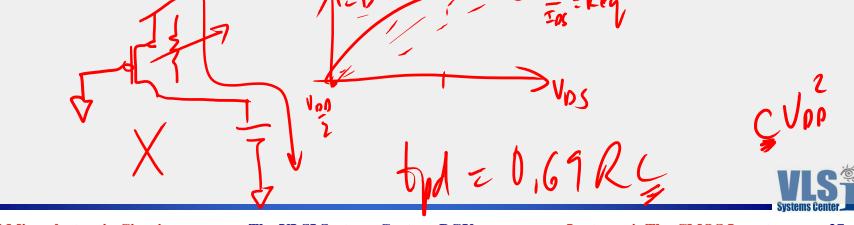

# t<sub>pd</sub> – equivalent resistance

- A good way to estimate the propagation delay is by finding the resistance of the MOSFET during the transition and using this resistance in quick calculations.

- The primary approach to deriving such an *equivalent resistance* is to calculate the transistor's average resistance throughout its operation (*ON*) period.

$$R_{eq} = average_{t=t_1...t_2} \left( R_{on}(t) \right) = \frac{1}{t_2 - t_1} \int_{t_1}^{t_2} R_{on}(t) dt = \frac{1}{t_2 - t_1} \int_{t_1}^{t_2} \frac{V_{DS}(t)}{I_{DS}(t)} dt$$

$$\approx \frac{1}{2} \left[ R_{on}(t_1) + R_{on}(t_2) \right]$$

## t<sub>pd</sub> – equivalent resistance

- □ Now, we will calculate the *propagation delay* of a *short channel* inverter, by using the equivalent resistance to discharge a capacitor from  $V_{DD}$  to  $V_{DD}/2$ .

- Assuming V<sub>DD</sub>>>V<sub>DSATn</sub>, we can assume that throughout the propagation delay, the transistor is velocity saturated.

• We can write:

$$R_{eq} = \frac{1}{V_{DD}/2} \int_{V_{DD}/2}^{V_{DD}} \frac{V_{DS}}{I_{DSAT} (1 + \lambda V_{DS})} dV_{DS} \approx \frac{3}{4} \frac{V_{DD}}{I_{DSAT}} \left(1 - \frac{7}{9} \lambda V_{DD}\right)$$

$$I_{DSAT} = k_n \left[ \left( V_{DD} - V_T \right) V_{DSAT} - \frac{V_{DSAT}^2}{2} \right]$$

**Digital Microelectronic Circuits**

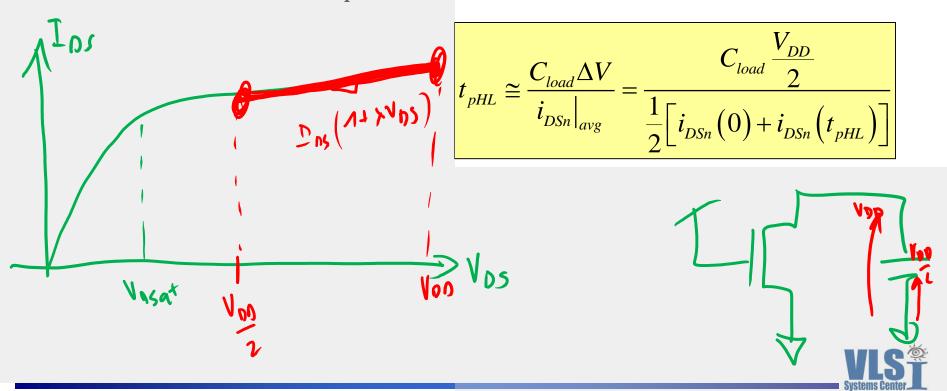

□ For example, if VDD=1.8V:

$$I_{DSATn} = k_n \left[ V_{GTn} V_{DSatn} - 0.5 V_{DSatn}^2 \right]$$

$= 115 \mu \frac{0.18 \mu}{0.18 \mu} \cdot (1.37 \cdot 0.63 - 0.5 \cdot 0.63^2) = 76.43 \mu A$

$R_{eqn} \approx \frac{3}{4} \frac{V_{DD}}{I_{DSAT}} \left( 1 - \frac{7}{9} \lambda V_{DD} \right)$

$= \frac{3}{4} \frac{1.8}{76.43 \mu A} \left( 1 - \frac{7}{9} 0.06 \cdot 1.8 \right) = 16.18 k \Omega$

**Digital Microelectronic Circuits**

## t<sub>pd</sub> – equivalent resistance

□ So all we need is to use our "magic" equation:

$$t_{pdHL} = 0.69R_{eqn}C_L = 0.69 \cdot 16.18k \cdot 1.5f = 16.75\,ps$$

$\Box$  Remember that for t<sub>pd</sub>, we also need R<sub>eqp</sub> for:

$$t_{pd} \triangleq \frac{t_{pLH} + t_{pHL}}{2} = \frac{0.69C_{load} \left(R_{eqp} + R_{eqn}\right)}{2}$$

**Digital Microelectronic Circuits**

## t<sub>pd</sub> – equivalent resistance

□ To calculate and analyze the parameters that affect the propagation delay, we will take  $\lambda = 0$  and get:

$$t_{pHL} = 0.69C_{load} \frac{3}{4} \frac{V_{DD}}{I_{DSATn}} = 0.52 \frac{V_{DD}C_{load}}{k_n V_{DSATn} \left(V_{DD} - V_{Tn} - \frac{V_{DSAT}}{2}\right)}$$

5.5 r

Accordingly, we can minimize the delay in the following ways:

» Minimize

$$C_{load}$$

.

» Increase  $W/L \longrightarrow C_{min}$

» Increase  $V_{DD}$

## **Last Lecture**

- So we saw that to reduce the propagation delay, we need to increase the device sizes (W/L).

- But how much should we increase them? What are the tradeoffs?

- □ For this, we will discuss two sizing parameters:

- » Beta Ratio (β)

- » Upsizing Factor (S) <---

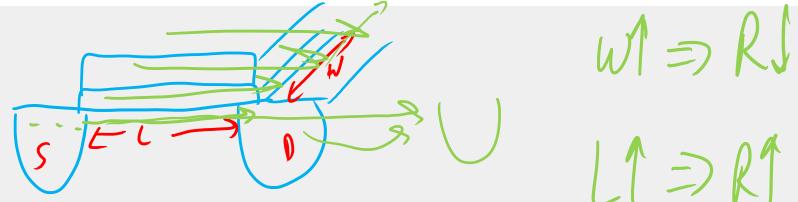

## What happens when we upsize a transistor?

□ Effective resistance decreases:

## □ Gate and Drain Capacitance increase:

- Device Sizing is the Width to Length ratio (W/L) of the transistor.

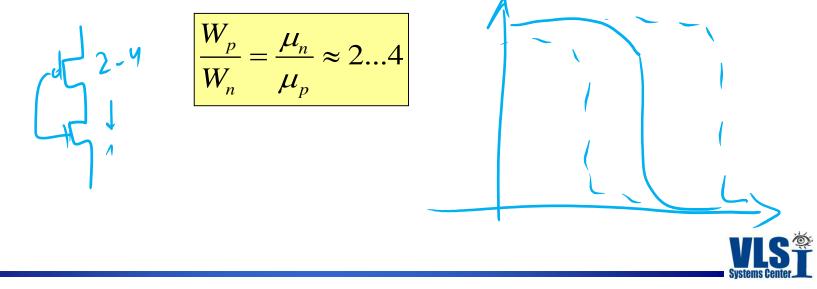

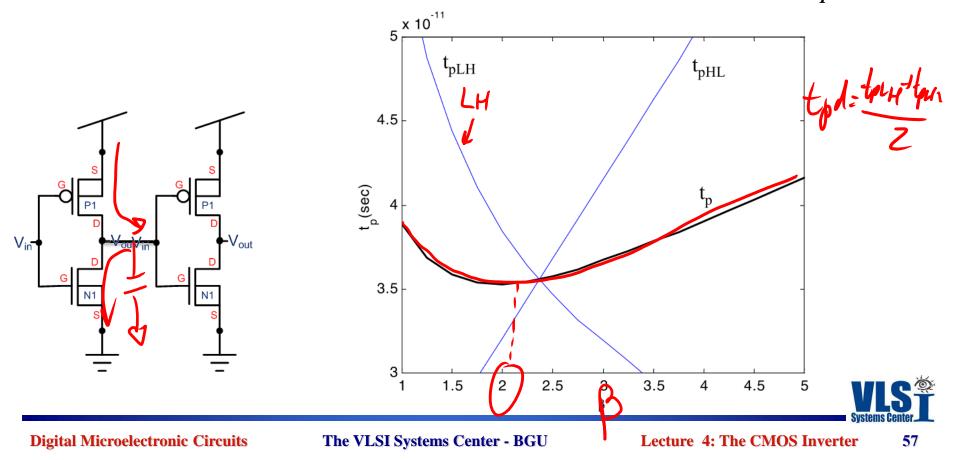

- □ When discussing a CMOS logic gate, we relate to the *pMOS/nMOS* ratio  $((W_p/L_p)/(W_n/L_n))$ .

- » We will call this ratio  $\beta$ .

- □ To get a *balanced* inverter (i.e.  $V_m = V_{DD}/2$ ) we usually will need  $\beta = 3-3.5$ , mainly due to the mobility ratio of holes and electrons.

- This generally equates the propagation delay of *High-to-Low* and *Low-to-High* transitions.

- However, this does not imply that this ratio yields the minimum overall propagation delay.

N.

56

[-

## **Device Sizing - β**

#### □ How can this be?

- » To get a faster  $t_{pLH}$ , we need to enlarge the pMOS width.

- » This increases the parasitic capacitance ( $C_{load}$ ), degrading  $t_{pHL}$ .

**Digital Microelectronic Circuits**

The VLSI Systems Center - BGU

Lecture 4: The CMOS Inverter 58

# **Device Sizing - β**

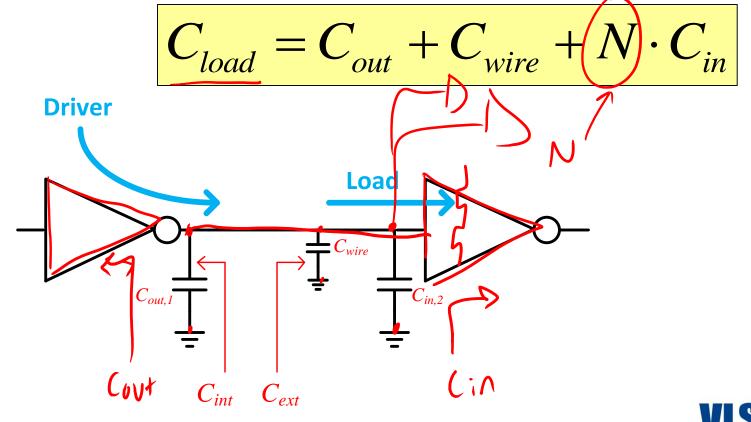

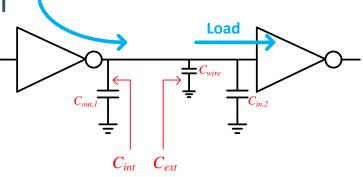

- We will now find the optimum ratio for sizing an inverter, considering two identical cascaded CMOS inverters.

- □ The load capacitance of the driving gate is:  $C_{load} = C_{out1} + C_{in2} + C_{wire}$

□ Assuming the input capacitance is the gate capacitance of the transistors ( $C_g$ ) and the output capacitance is the drain capacitance ( $C_d$ ), we can write:

$$C_{load} = (C_{dp1} + C_{dn1}) + (C_{gp2} + C_{gn2}) + C_{wire}$$

□ Assuming a linear dependence on device size, we get:

$$C_{load} = (1+\beta)(C_{dn1}+C_{gn2})+C_{wire}$$

Driver

□ Noting that we have reduced the equivalent resistance of the *pMOS* by  $\beta$ , we can write the first order *RC* propagation delay:  $t_{pd} = \frac{0.69C_{load}}{2} \left( R_{eqn} + R_{eqp} \right) = 0.345 \left[ (1 + \beta) (C_{dn1} + C_{gn2}) + C_{wire} \right] \left( R_{wire} + \frac{R_{wire}}{\beta} \right)$

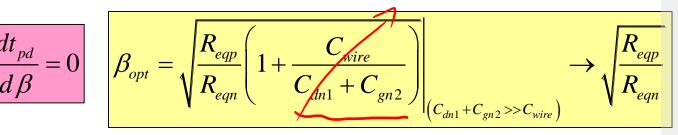

Device Sizing - β

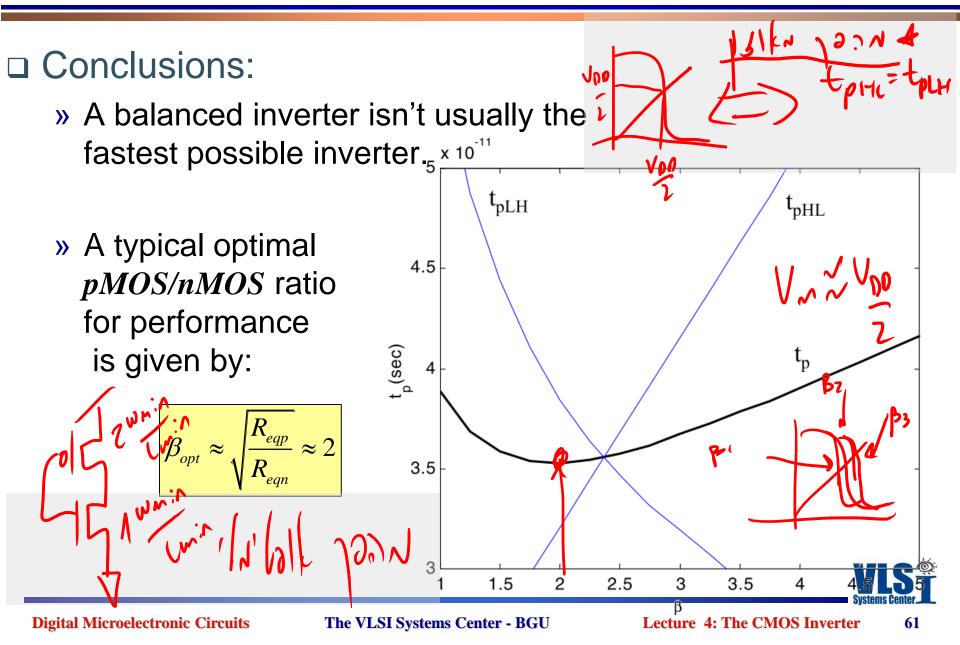

□ Now we just need to find the minimum:

$\Box$  A typical optimum for  $\beta$  is usually around 2.

## **Device Sizing - β**

We saw how the ratio between the *pMOS* and *nMOS* can be optimized to improve performance.

Now, we will take a balanced inverter and see how upsizing affects the *intrinsic* or *unloaded delay*.

We will start by writing the delay as a function of an intrinsic capacitance (diffusion and overlap) and the extrinsic capacitances (fanout and wiring):

$$C_{load} = C_{int} + C_{ext}$$

$$t_{pd} = 0.69R_{eq}C_{load} = 0.69R_{eq}(C_{int} + C_{ext})$$

**Digital Microelectronic Circuits**

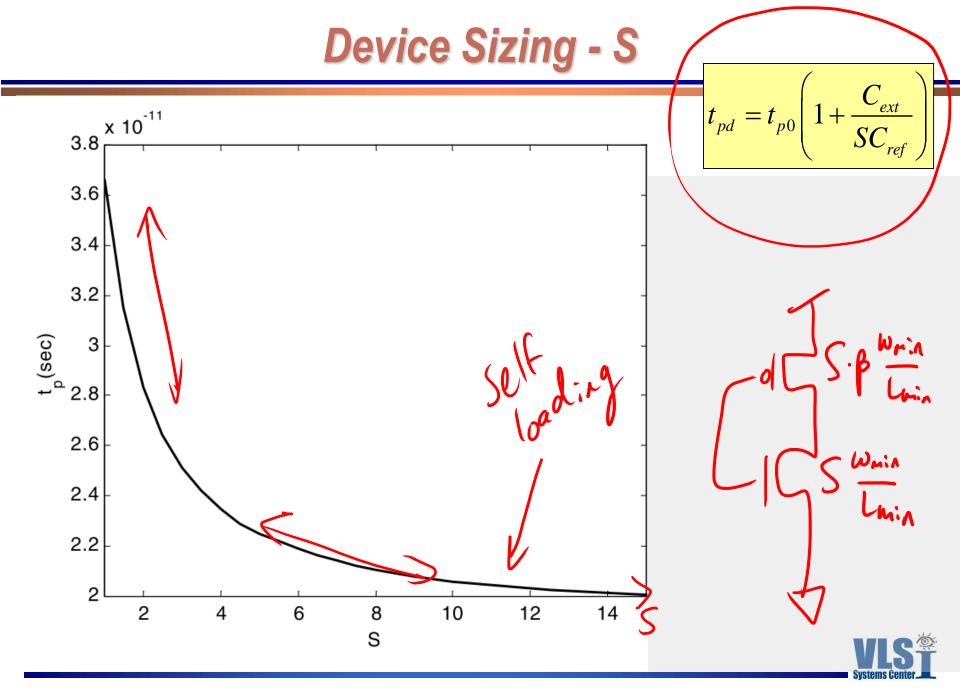

## **Device Sizing - S**

- $\Box$  Now, we will mark the minimal intrinsic delay as  $t_{p0}$ . This is the delay of a minimum sized balanced inverter only loaded by its own intrinsic capacitance  $(C_{oxt}=0)$ :  $= 0.69 R_{..}$

- □ We will now mark the *sizing factor*, S. This is the relative upsizing of the inverter, i.e.  $C_{int} = SC_{ref}$  and accordingly  $R_{eq} = R_{ref}/S$ .

- Now we can write the delay of an upsized inverter:

$$t_{pd} = 0.69R_{eq} \left( C_{int} + C_{ext} \right) = 0.69 \frac{R_{ref}}{S} \left( SC_{ref} + C_{ext} \right)$$

$$= 0.69R_{ref} C_{iref} \left( 1 + \frac{C_{ext}}{SC_{ref}} \right) = t_{p0} \left( 1 + \frac{C_{ext}}{SC_{ref}} \right)$$

*p*0

**Digital Microelectronic Circuits**

**Digital Microelectronic Circuits**

## **Device Sizing - S**

# $t_{pd} = t_{p0} \left( 1 + \frac{C_{ext}}{SC_{ref}} \right)$

## □ Conclusions:

- » The intrinsic delay of an inverter  $(t_{p0})$  is independent of the sizing of the gate and is purely determined by technology. When no load is present, an increase in the drive of the gate is totally offset by the increased capacitance.

- » To minimize a loaded inverter's delay, *S* should be enlarged, but at the expense of a substantial gain in area.

- We can calculate t<sub>pd</sub> in several ways, but the easiest is to measure the equivalent resistance during a typical transition.

- One of our main techniques to improve the delay is through transistor sizing, which we discussed in two fashions:

- » Setting the optimal ratio between the PUN/PDN.

- » Upsizing the gate to deal with a large output load.

**Digital Microelectronic Circuits**

And now that we fully understand the static and dynamic operation of the CMOS Inverter, it's time to take a look at

# **POWER CONSUMPTION**

## **Dynamic Power**

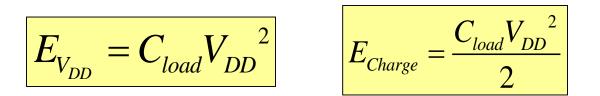

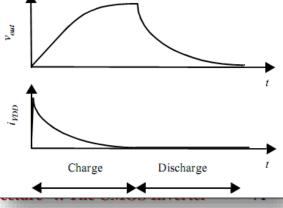

Assuming an ideal step input, we can analyze the energy consumed from the supply of the equivalent circuit during a *Low-to-High* transition is given by:

$$E_{V_{DD}} = \int_{0}^{\infty} i_{V_{DD}}(t) V_{DD} dt = V_{DD} \int_{0}^{\infty} C_{load} \frac{dV_{out}}{dt} dt = C_{load} V_{DD} \int_{0}^{V_{DD}} dV_{out} = C_{load} V_{DD}^{2}$$

Now, looking at the energy stored in the load capacitance, we get:

$$E_{Charge} = \int_{0}^{\infty} \dot{i}_{V_{DD}}(t) V_{out} dt = \int_{0}^{\infty} C_{load} \frac{dV_{out}}{dt} V_{out} dt = C_{load} \int_{0}^{V_{DD}} V_{out} dV_{out} = \frac{C_{load} V_{DD}^{2}}{2}$$

1(1)

$V_{DD}$

i<sub>VDD</sub>

## **Dynamic Power**

Analyzing these results, we see that the energy required to charge the output capacitance is *twice* the energy stored on the capacitor at the end of the transition.

Assuming the input changes now from zero to one, we now get a High-to-Low transition.

□ Here, the supply is disconnected, and the charge stored  $\overline{2}$  on the capacitance flows through the *nMOS* to the ground.

Dynamic Power 🏼 🖊 🗖 🚽

C .O

$C_{load}V_{DD}$

Discharge

$V_{out}dV$

Charge

out

ivon

The energy dissipated is the total energy stored on the output capacitance, as no charge is left:

$$E_{discharge} = \int_0^\infty i_{DSn}(t) V_{out} dt = \int_0^\infty C_{load} \frac{dV_{out}}{dt} V_{out} dt = C_{load} \int_{V_1}^0 V_{out} dt$$

The sum of the charge and discharge energy is obviously equal to the energy supplied:

$$E_{charge} + E_{discharge} = E_{V_{DD}} = C_{load} V_{DD}^{2}$$

**Digital Microelectronic Circuits**

## **Dynamic Power**

#### Conclusions:

- » Each charge and discharge cycle dissipates a fixed amount of energy, independent of the size of the device.

- » The effective energy is the charge stored on the capacitance. The rest of the energy is wasted as heat burned on the pMOS (charge) and nMOS (discharge) resistance.

- □ To compute the *Power Dissipation*, we calculate the total energy wasted per one second.

- □ For a circuit that completes a *Low-to-High* transition  $f_{0 \rightarrow 1}$ times per second (and therefore a *High-to-Low* transition as well...), the dynamic power consumption is:

$$P_{dyn} = C_{load} V_{DD}^2 \cdot f_{0,1}$$

## **Dynamic Power**

- We said that the *Power Dissipation* is a factor of the switching frequency of the gate.

- But the gate only switches when its input changes. In other words, the *switching activity* is smaller than the circuit frequency.

- We can rewrite the *Dynamic Power* expression using the *activity factor*, α of the inverter,

$$P_{dyn} = C_{load} V_{DD}^{2} \cdot f \cdot \alpha = C_{eff} V_{DD}^{2} f$$

C<sub>eff</sub> is the effective capacitance of a complex circuit, describing the average capacitance that actually switches each cycle.

Fdyn = CVD

d ~ Aol

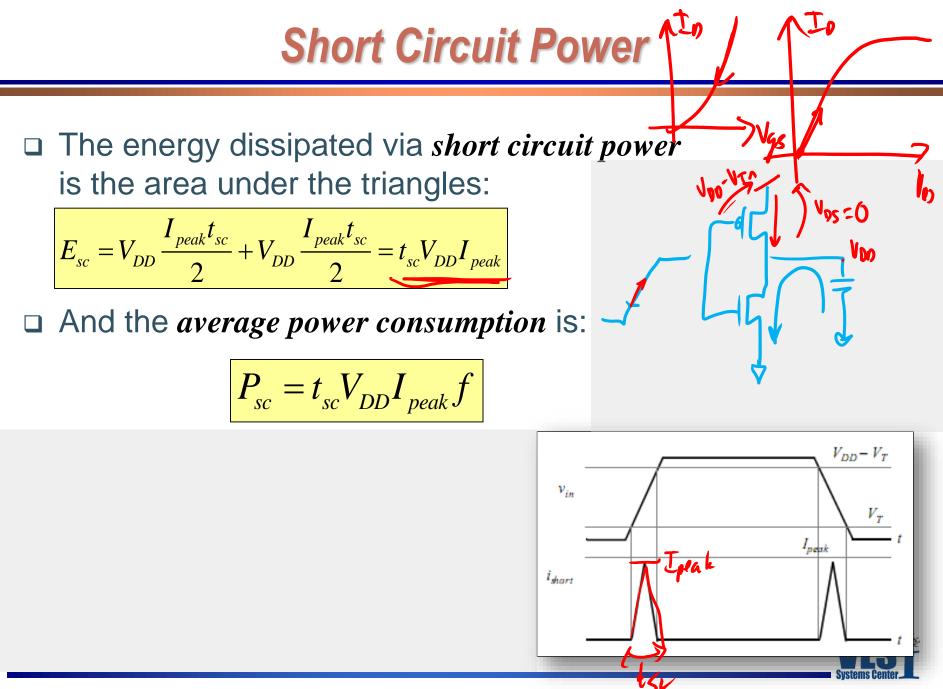

## **Short Circuit Power**

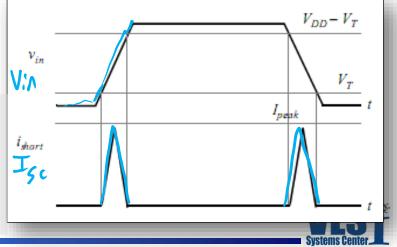

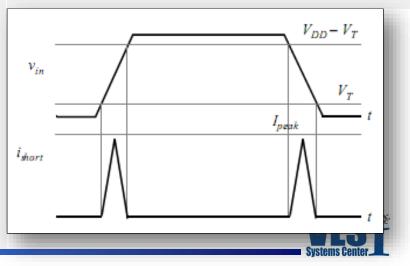

- During the above analysis, the input was an *ideal step function*, immediately closing one transistor when the other was opened.

- In a real circuit, the input signal has a non-zero rise/fall time, resulting in a time interval with both the pMOS and nMOS transistors open.

- □ This provides a direct path from *V*<sub>DD</sub> to *GND*, with a current known as *Short Circuit* current.

- This is shown in the following waveforms:

**Digital Microelectronic Circuits**

The VLSI Systems Center - BGU

Lecture 4: The CMOS Inverter 74

- □ The short circuit interval,  $t_{sc}$ , is the margin between the threshold voltages of the transistors.

- □ Assuming a linear input transition:

$$t_{sc} = \frac{V_{DD} - 2V_T}{V_{DD}} \cdot \frac{t_{rise(fall)}}{0.8}$$

**Digital Microelectronic Circuits**

## **Short Circuit Power**

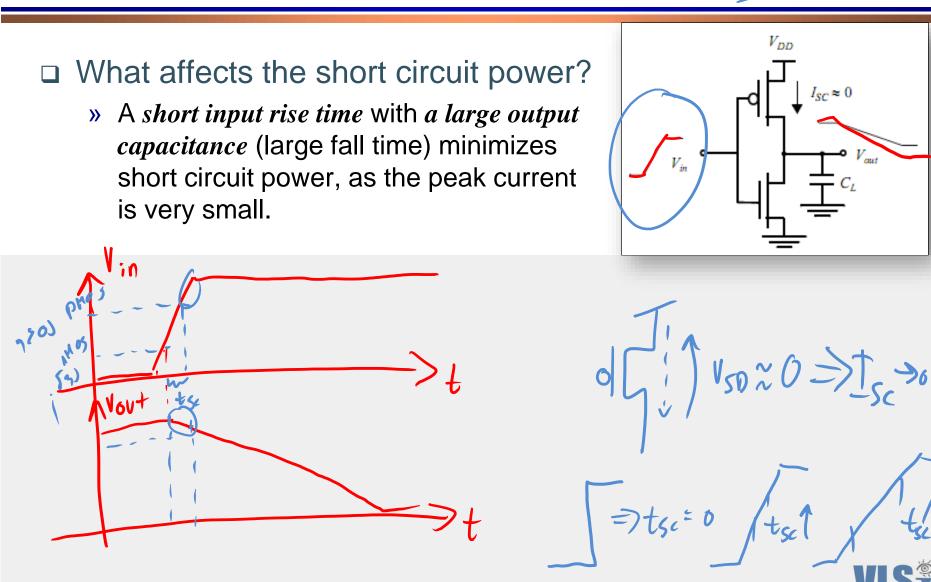

## **Short Circuit Power**

#### ממ □ What affects the short circuit power? SC≈ IMAX small output capacitance relative to the **>>** *input rise time* causes extensive short circuit power, as the peak current is maximal (saturation current of the transistors). Vout m Vout=0 □ Conclusion:

» Try to keep the input and output rise/fall times similar to maximize performance and minimize short circuit power.

## **Static Power**

□ Ideally, a MOSFET transistor is a *perfect switch*.

- In such a case, a CMOS inverter never has a conducting path in steady state, resulting in no static power dissipation.

- However, in reality, MOSFET transistors never completely turn off.

Istatic=L

□ Since static power is *constantly consumed*, the power dissipation can be simply expressed as:

$$P_{static} = I_{static} V_{DD}$$

Sources of static power are beyond the scope of this course, however they are quickly becoming the *dominant* source of power in advanced sub-micron technologies.

#### □ For further probing, see these subjects:

- » Subthreshold current <

- » Hot Electrons ✓

- » DIBL 🗸

- » Punchthrough

79

- As we saw above, there are three components to the *power* dissipation of a CMOS inverter:

- » Dynamic Power

- » Short Circuit Power

- » Static Power

- Putting them all together, we get the *total power* consumption of a CMOS logic gate:

$$P_{total} = P_{dyn} + P_{sc} + P_{static} = \alpha f C_{load} V_{DD}^{2} + \alpha f V_{DD} I_{peak} t_{sc} + V_{DD} I_{static}$$

We previously learned that the *power-delay-product* (*PDP*) measures the average energy of a switching event:

$$PDP = P_{dyn} \cdot t_{pd} = C_{load} V_{DD}^{2} f_{max} t_{pd} = \frac{1}{2} C_{load} V_{DD}^{2}$$

Since both *Power* and *PDP* give a clear advantage to energy reduction versus performance, we measure the *energy-delay-product* (*EDP*) as a combined measurement of the two:

$$EDP = PDP \cdot t_{pd} = \frac{1}{2}C_{load}V_{DD}^{2}t_{pd}$$

4.1 An Intuitive Explanation

#### 4.2 Static Operation

4.3 Dynamic Operation

**4.4 Power Consumption**

4.5 Summary

Okay, enough with the inverter. But before we go on, let's go over a short

## **SUMMARY**

# Summary

## □ The CMOS inverter is characterized by:

- » A *pMOS* Pull-Up device and an *nMOS* pull down device.

- » The *pMOS* is usually wider due to inferior current driving.

- » An almost ideal VTC with a *full rail to rail swing*.

- » Noise margins of a balanced inverter are close to  $V_{DD}/2$

- » The steady state response is not affected by *fanout*.

- Propagation delay:

- » Can be approximated as:

- » Small loads make faster drivers.

- » Widening the transistors improves the delay.

- Power Dissipation:

- » Dominated by *dynamic power*, given by:

- > Short circuit power can be reduced by equating input/output slopes.

$t_{pd} = 0.69C_{load} \left( \frac{R_{eqp} + R_{eqn}}{2} \right)$

» Static Power is a problem out of the scope of this course.