# Digital Microelectronic Circuits (361-1-3021)

Presented by: Adam Teman

Lecture 2: Terminology and Design Metrics

1

**Digital Microelectronic Circuits**

#### Last Week

#### Introduction

- » Moore's Law

- » History of Computers

#### □ Circuit analysis review

- » Thevenin, Norton

- » First order RC circuits

- » Boolean Algebra

In this course we will discuss former and current methods of digital circuit implementation.

In order to analyze the methods, understand their pros and cons, and compare them, we need a "toolbox" of terms and metrics.

In this lecture, we will learn the general concepts used in the development of digital circuits and the primary metrics used to compare them.

#### What will we learn today?

2.1 Switching Concept

**2.2 Static Metrics**

**2.3 Dynamic Metrics**

**2.4 Power Consumption**

4

**Digital Microelectronic Circuits**

This course is about *Digital Circuits*. So what is the difference between

# ANALOG VS. DIGITAL

## Analog vs. Digital

□ Analog Electronics:

- » Systems with a *continuously variable* signal.

- Digital Electronics:

- » Signals with *discrete* (usually Boolean) *levels*.

#### □ Mixed Signal:

» A combination of digital and analog components.

#### □ The real world is Analog!

- » Digital systems map a range of Analog levels into discrete values.

- » This is also known as quantization.

- Both Analog and Digital systems can be used to perform almost every type of processing:

- » Addition/Multiplication.

- » Filters.

- » Limiters.

- » etc.

Digital Systems are much less susceptible to noise and therefore, in general, whatever can be made digital is made digital.

## Analog vs. Digital: Pros and Cons

#### □ Noise:

- » Analog systems amplify noise and are limited by noise.

- » Digital systems have large *noise margins* and *signal regeneration*.

#### □ Precision:

- » Precision of analog systems is usually limited by the noise floor.

- » Precision of digital systems is limited by bit depth.

- » Digital systems inherently suffer from a *quantization error*.

## Analog vs. Digital: Pros and Cons

#### □ Speed:

- » Analog systems can usually perform computations almost immediately.

- » Digital systems may need several levels/iterations to complete a computation.

#### Design Difficulty:

- » Analog Design is an "art" it is very hard to logically automate.

- » Digital Design is relatively straightforward, and therefore can often be logically defined and automated.

## What is Noise (in Digital Circuits)?

- Digital gates map analog levels (currents/voltages) into discrete (Boolean) values (1's and 0's).

- □ Noise (in the context of digital circuits) means:

- » "Unwanted variations of voltages or currents at the logic nodes"

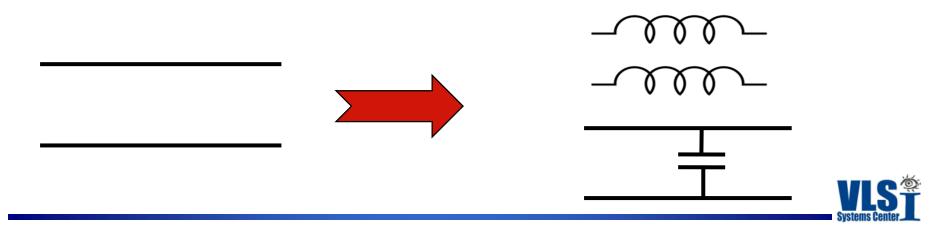

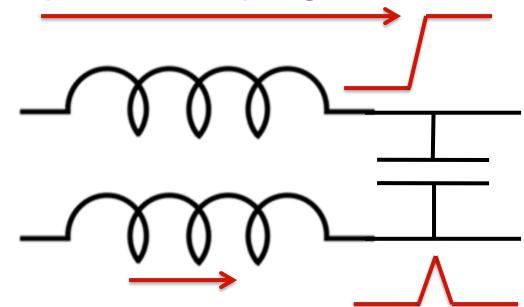

- This can happen for various reasons, such as coupling between two wires:

## **Noise in Digital Gates**

- A change in current causes current noise due to inductive coupling.

- A change in voltage causes voltage noise due to capacitive coupling.

### **Noise in Digital Gates**

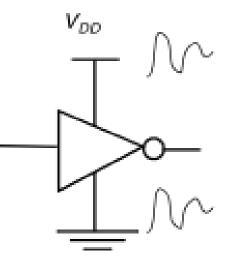

Another common source of noise is due to nonidealities of Voltage Sources.

» For example, right after clock edges.

**Digital Microelectronic Circuits**

## **Example: Transmitting a Signal**

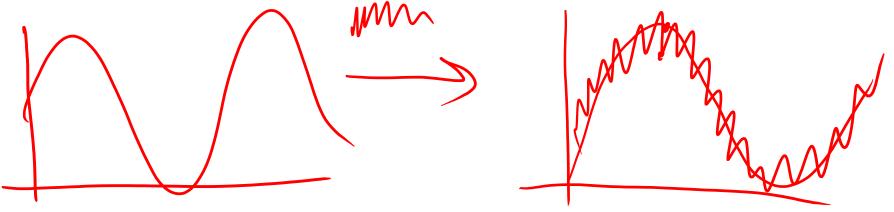

What happens when noise is applied to an analog signal?

## **Example: Transmitting a Signal**

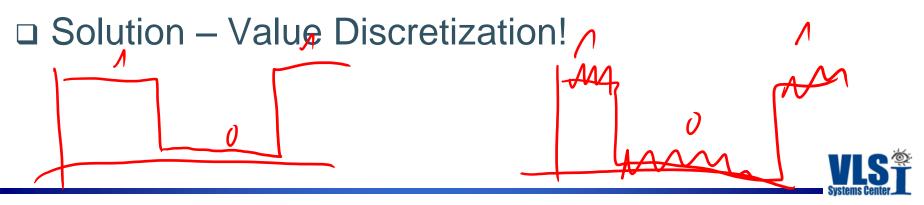

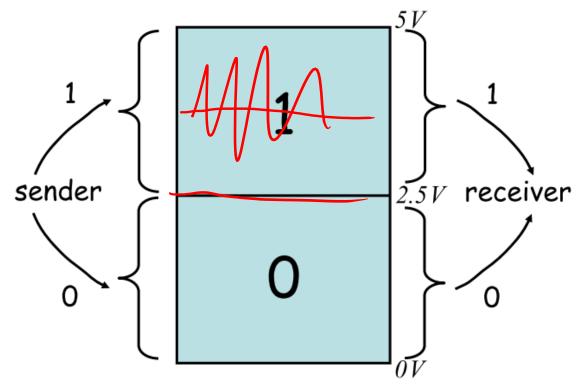

If we discretize the value, we have some noise immunity:

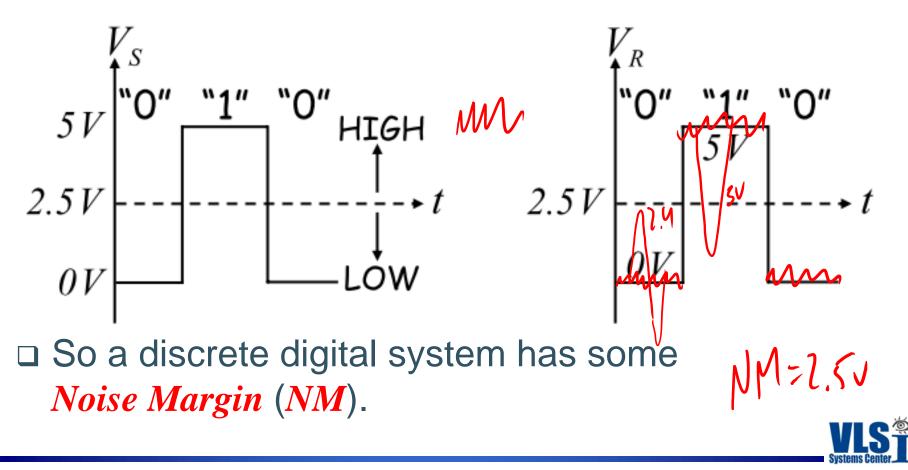

We can give a preliminary definition of the preceding system's noise margins:

□ But what if the sender transmits 2.5V?

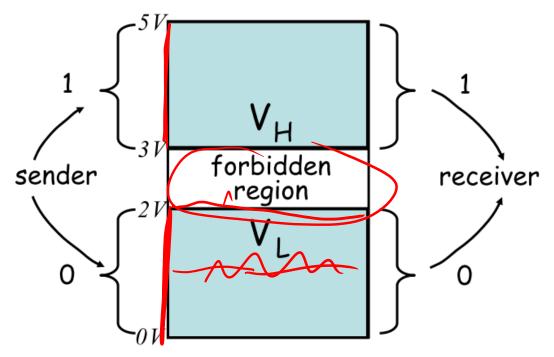

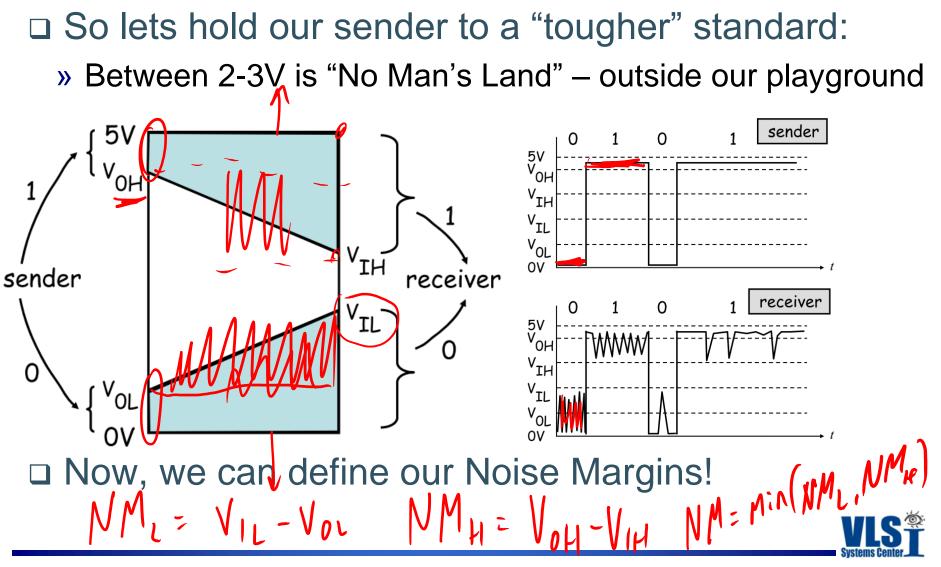

□ So a better way is to define a "Discipline":

» Between 2-3V is "No Man's Land" – outside our playground

But what noise can be tolerated if the sender transmits 2V?

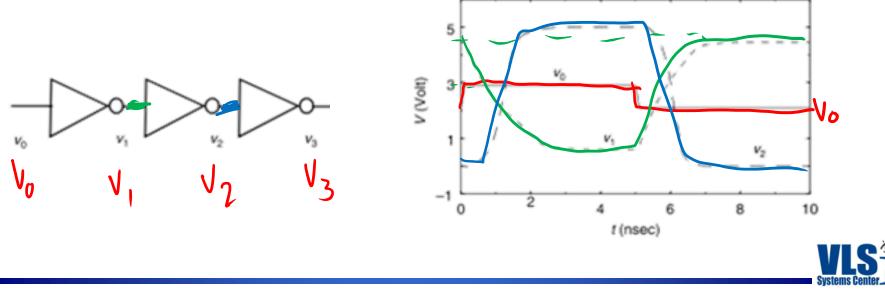

- One of the ways that digital systems deal with noise is through Signal Regeneration.

- A digital gate with a *Regenerative Property* will cause noise to "disappear" after propagating through several stages.

In order to be considered "Digital", a logic gate must have the following properties:

- » A Boolean functionality

- i.e. Distinctive '1' and '0' output for any digital input.

- » Unidirectionality.

- The signal cannot flow from the output to the input.

- » Positive Noise Margins.

- When the output is a '1', the next input knows it is a '1'.

- » Regenerative Property

- Any noise will "disappear" within a few stages.

So before we start we need to understand the basic

## **SWITCHING CONCEPT**

We've learned all about *Boolean Algebra*.

We've built *theoretical building blocks* for calculating *any function*.

Now, how do we turn the theoretical blocks into actual components?

#### Take a light switch as an example of *Boolean Logic*:

**Digital Microelectronic Circuits**

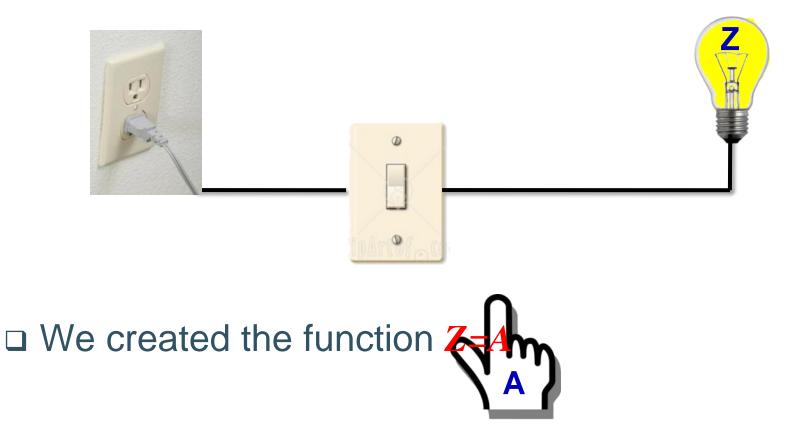

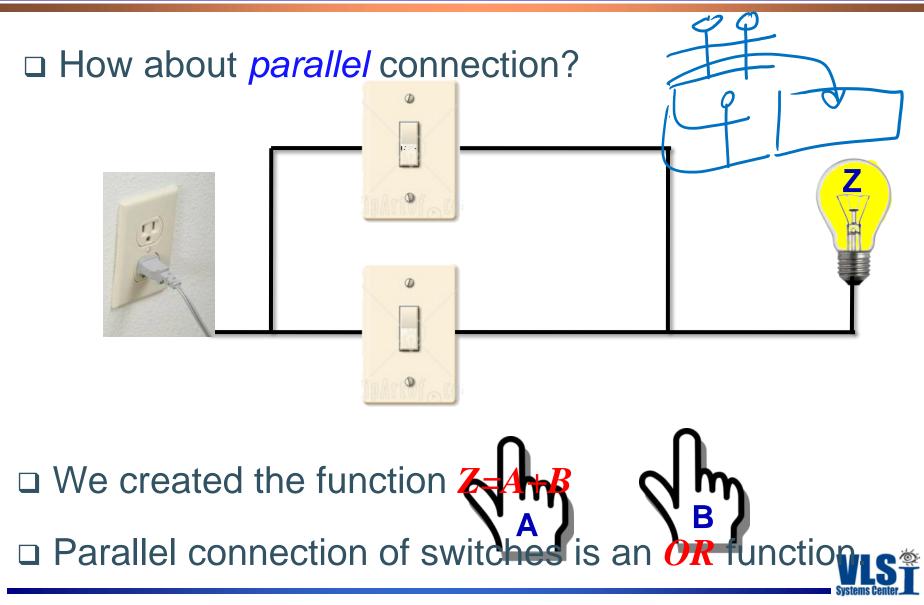

#### □ What happens if we connect two switches *serially*?

**Digital Microelectronic Circuits**

**Digital Microelectronic Circuits**

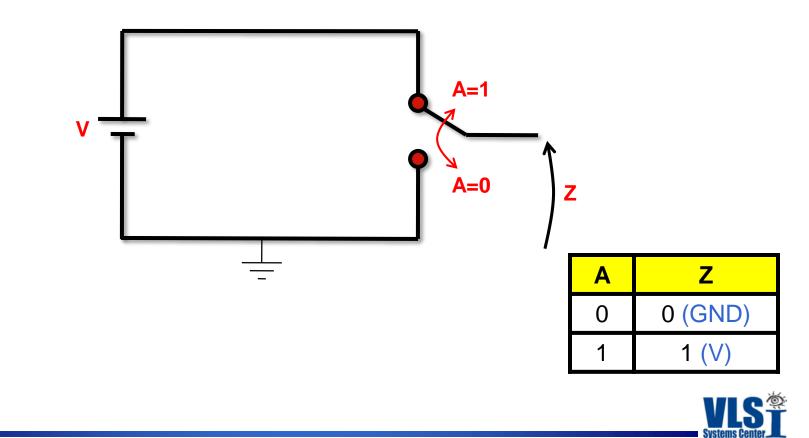

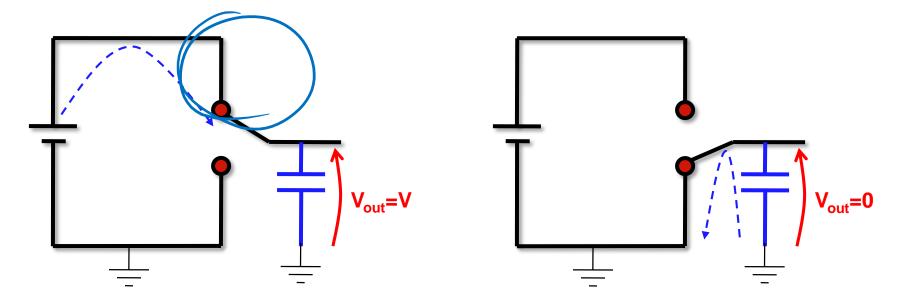

□ We can now look at a switch in an electrical circuit:

**Digital Microelectronic Circuits**

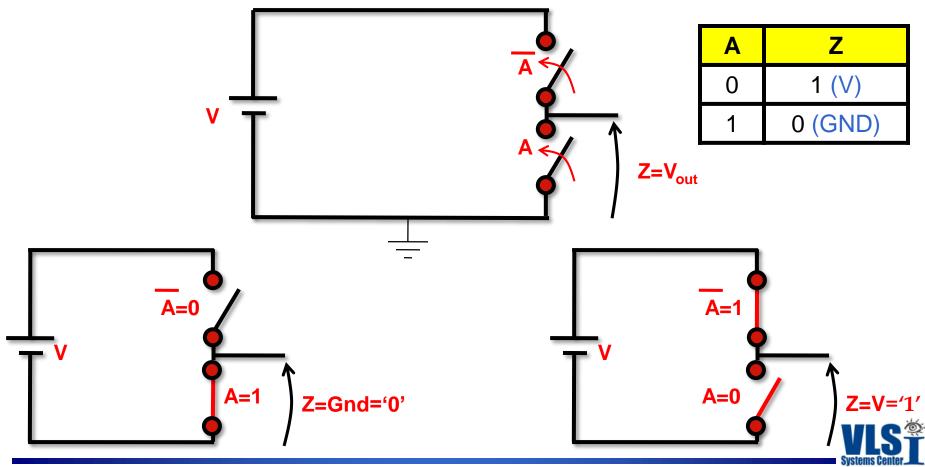

Using serially connected complementary switches, we can easily create *Inverting Logic*:

**Digital Microelectronic Circuits**

- This circuit is called an "*Inverter*", as it turns a high input into a low output and vice versa.

- □ Logically, this is a *NOT* gate!

- The *Inverter* is the basic circuit in digital design. All of our definitions and analyses will be developed based on the *Inverter*.

**Digital Microelectronic Circuits**

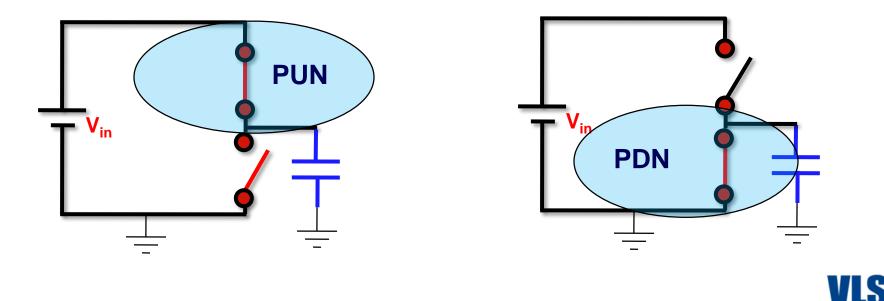

Logic levels in digital circuits are generally achieved by *charging* or *discharging* a capacitor.

- The capacitor is generally charged through what is known as a Pull Up Network (PUN).

- □ The capacitor is generally *discharged* through what is known as a *Pull Down Network* (*PDN*).

- We will now analyze the switching according to two characteristic operation conditions:

- Dynamic Operation occurs after a change in the circuit causes a *Transient*.

- » All currents and voltages are a function of time.

- » Capacitors adhere to their differential equations.

- Static Operation occurs when the gate is in its Steady State.

- » The transient is finished at t= $\infty$ .

- » All capacitors are charged to a finite voltage and no current flows through them.

#### Using the VTC of an Inverter, we will introduce

# **STATIC METRICS OF LOGIC GATES**

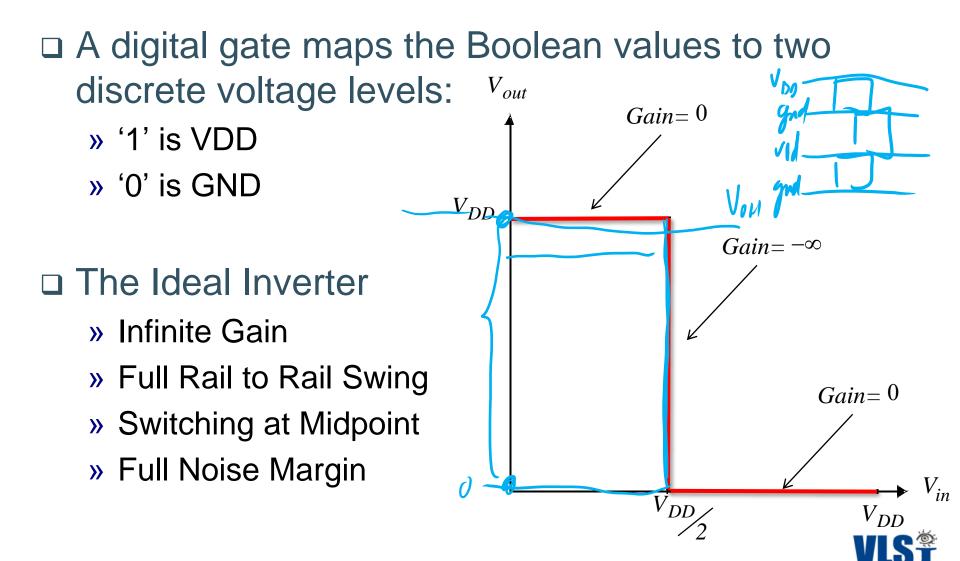

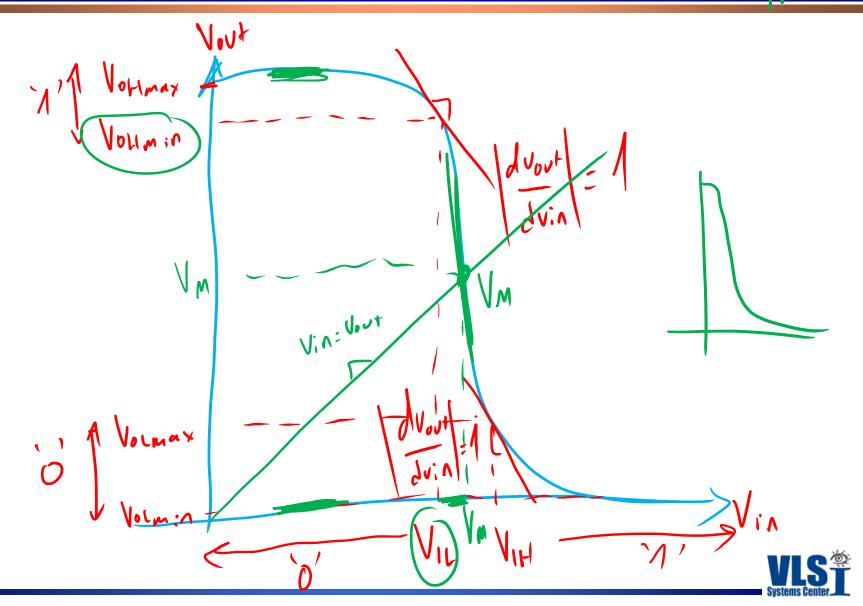

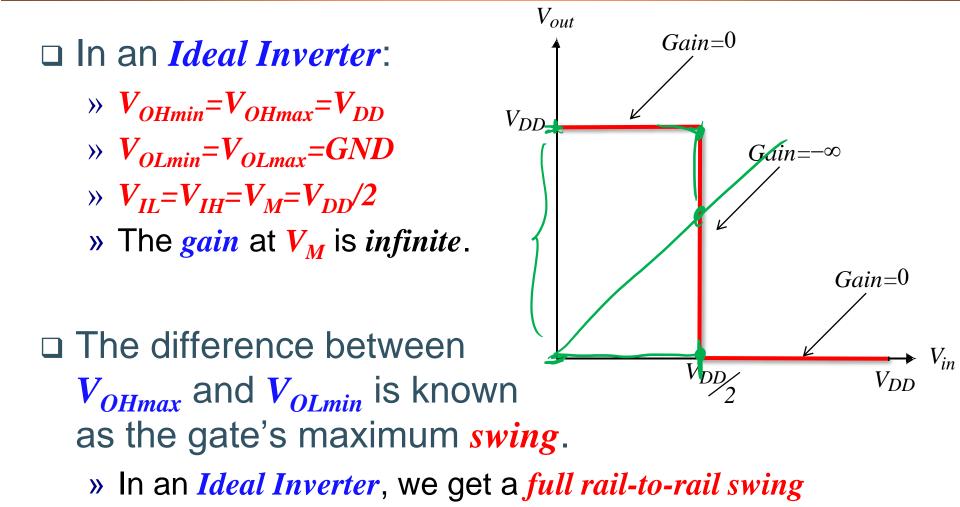

- All digital circuits and logic gates are characterized using a VTC (Voltage Transfer Characteristics) graph.

- » This is sometimes called the DC Transfer Characteristic.

- □ The *VTC* displays the reaction of a logic gate to a range of inputs.

- □ Since most of the logic gates we will learn about are voltage based, the *VTC* graph shows  $V_{out}/V_{in}$

- □ We will first look at the *VTC* of an *Ideal Inverter*.

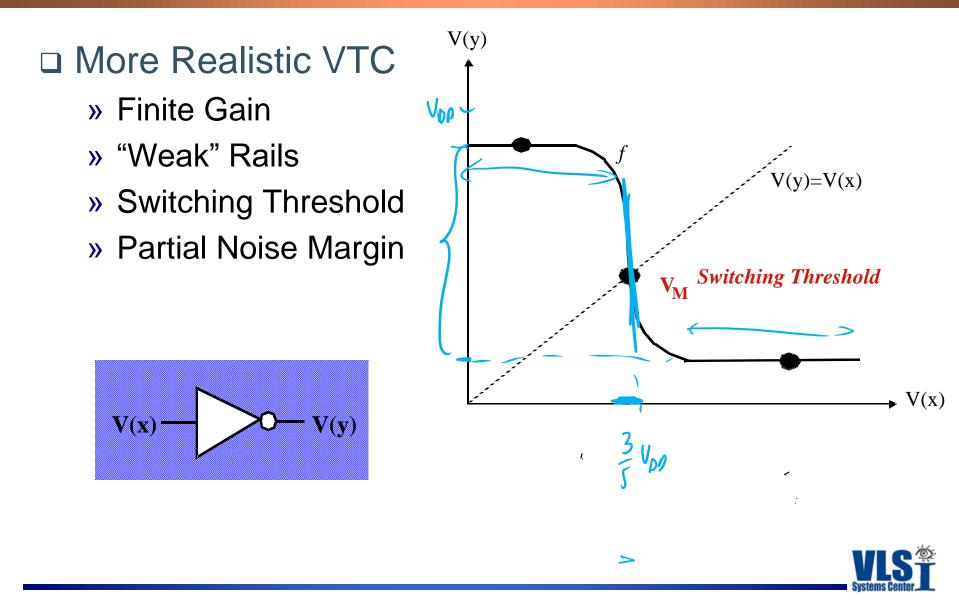

#### **Realistic Inverter VTC**

**Digital Microelectronic Circuits**

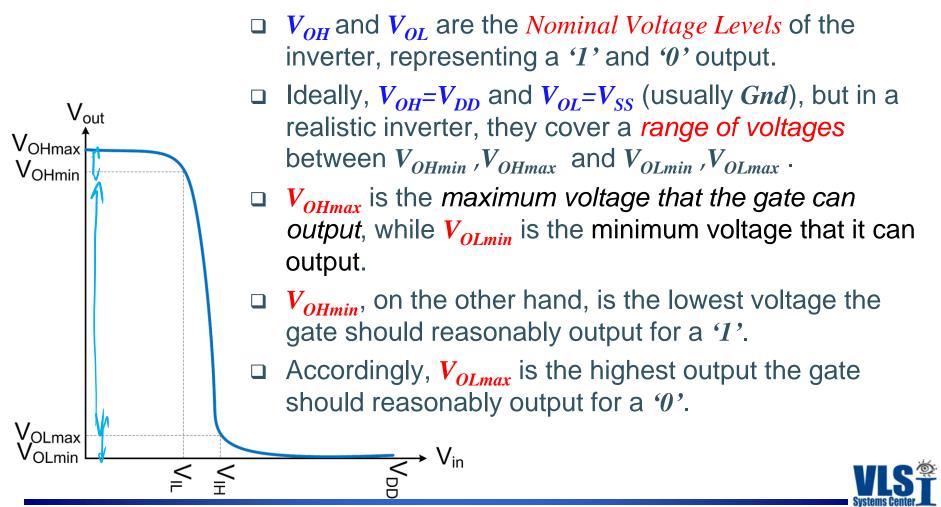

## **Nominal Voltage Levels**

#### □ Accordingly, let's define the *Nominal Voltage Levels*.

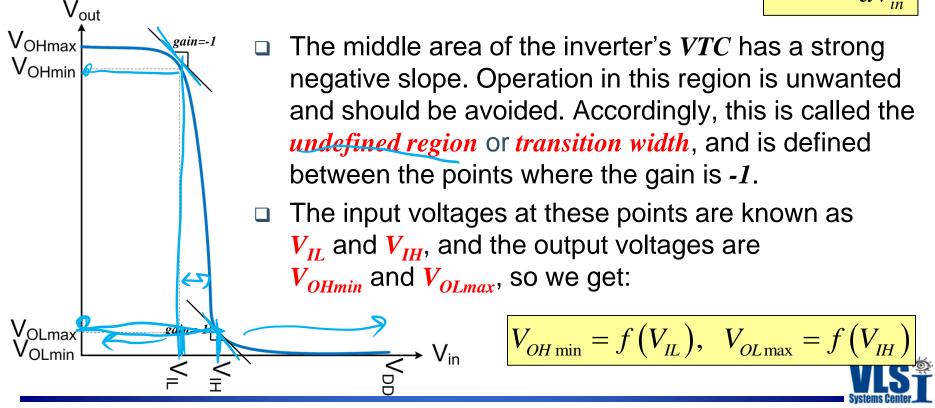

# □ To properly define $V_{OHmin}$ and $V_{OLmax}$ , we must first define *gain*.

□ The *gain* of a logical gate is defined as: *ga*

$$gain = \frac{dV_{out}}{dV_{in}}$$

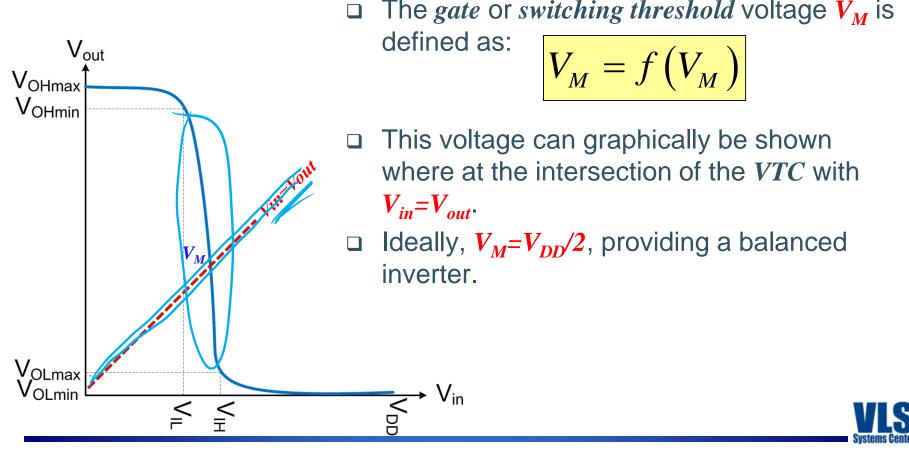

# □ We have one more important nominal voltage level, the *Switching Threshold*, *V*<sub>M</sub>.

### Summary of Nominal Voltages \*

# **Nominal Voltage Levels**

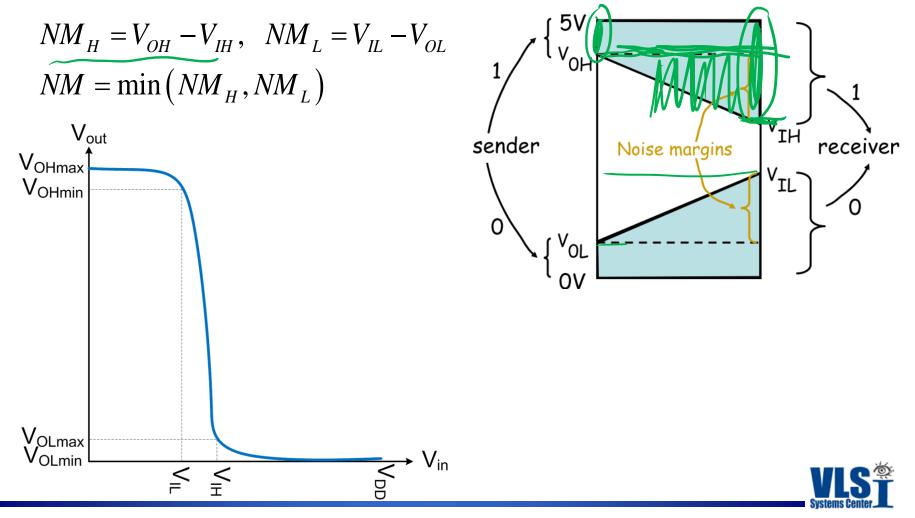

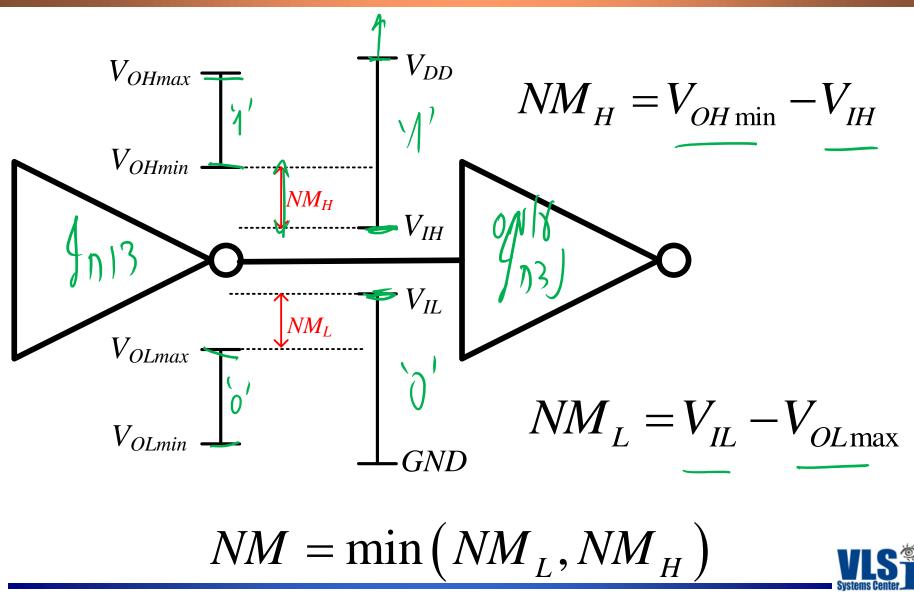

# Noise Margins

□ Remember our definition of Noise Margins?

# **Noise Margins**

**Digital Microelectronic Circuits**

The VLSI Systems Center - BGU

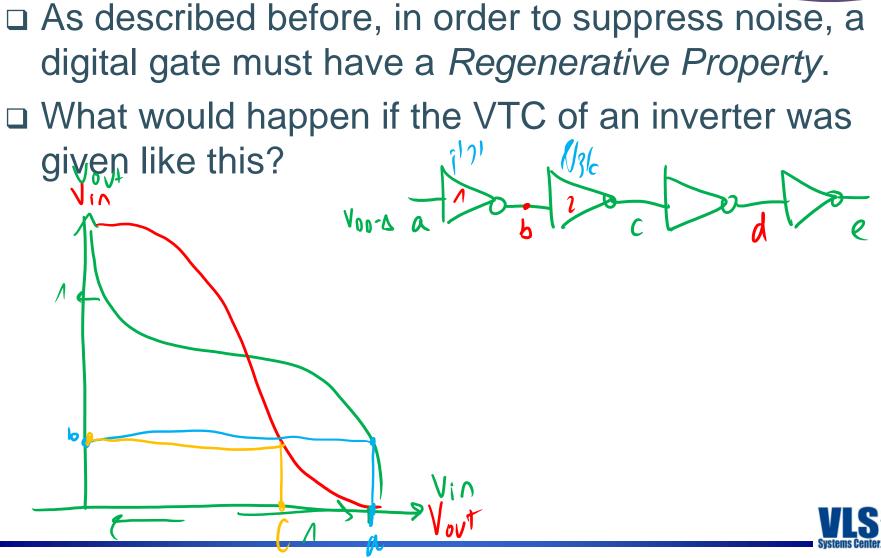

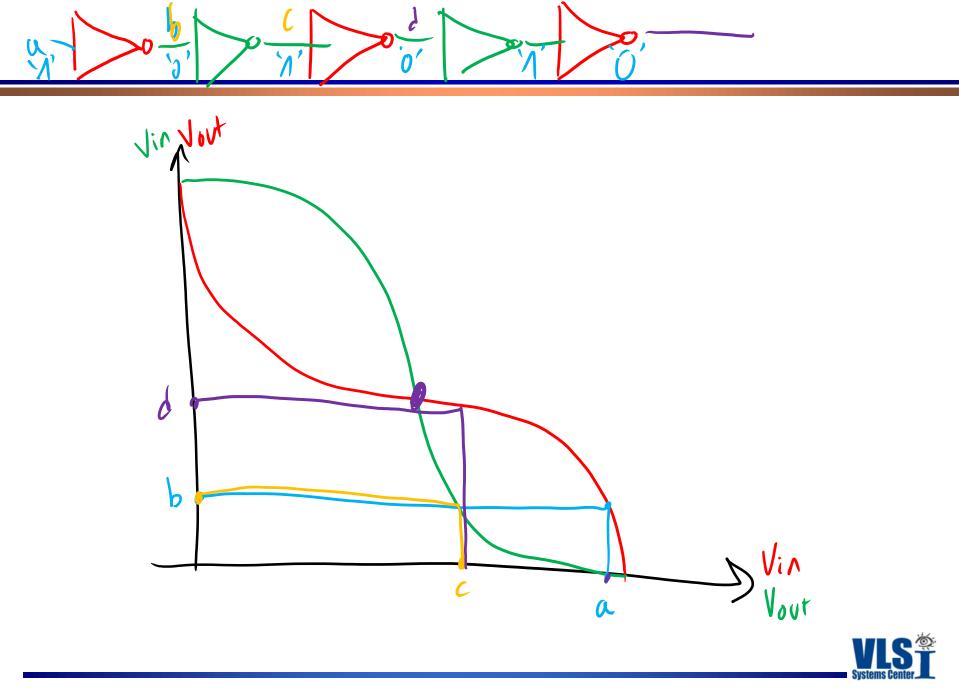

### **Regenerative Property**

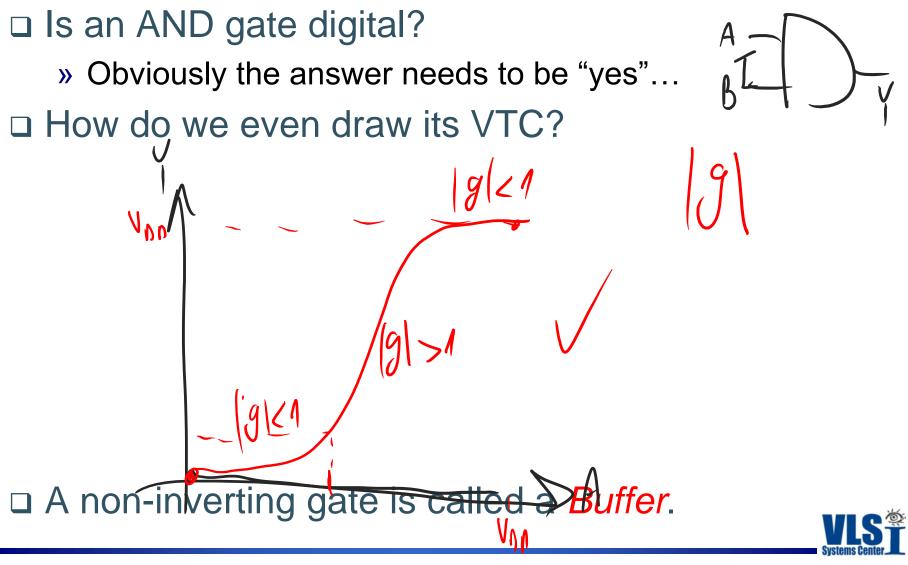

In order to ensure a Regenerative Property, the VTC must have three regions: |g|'V ofe » |g|**>**1 » /g/<1 6 N: N Vost ()

### What about an AND Gate?

### **Additional Characteristics**

□ Fan In

» The *Fan In* of a gate is the number of inputs to the gate.

- □ *Fan In* is a characteristic of the gate's function and not of the implementation.

- □ For example, the *Fan In* of an *inverter* is 1.

- □ The *Fan In* of a *2-input AND* gate is *2*.

- A large *Fan In* tends to make the gate more complex, resulting in inferior static and dynamic properties.

### **Additional Characteristics**

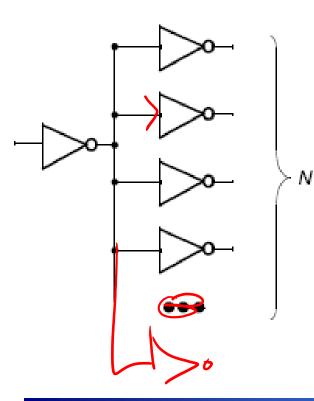

### □ Fan Out

» *Fan Out* denotes the number of load gates *N* that are connected to the output of the driving gate.  $FO_{max} = \frac{I_{out}}{I_{out}}$

- The maximum Fan Out of an ideal gate is infinity.

- The dynamic performance (speed) of the gate is effected by the *Fan Out*.

- □ In addition, the logic output level of a some real

- gates drop as the Fan Out is increased.

- To maximize *Fan Out*, the output resistance of the driving gate should be as small as possible (no voltage drop) and the input resistance of the load gates should be as large as possible (minimal input current).

### **Static Metrics - Summary**

###

- » VOH, VOL, Swing

- » VIH, VIL, gain, forbidden region

- » VM (switching threshold)

- Noise Margins

- □ Regenerative Property

- Fan In

- Fan Out

### **Last Lecture**

### □ Terminology:

- » Analog vs. Digital

- » Switching Concept

- » Pull up, Pull down, Fan In, Fan Out

### Static Metrics:

- » VTC, Nominal Voltage Levels

- » Noise Margins

<u>This hour:</u>

### Dynamic Metrics

- » Tpd, tr, tf

- Power and Energy

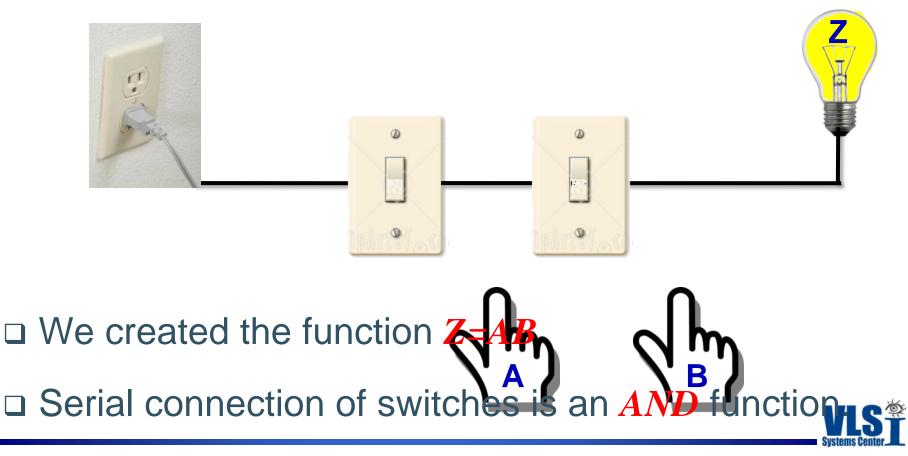

#### 2.0 Analog vs. Digital

2.1 Switching Concept

**2.2 Static Metrics**

**2.3 Dynamic Metrics**

**2.4 Power Consumption**

To compare the performance of a logic gate we will now look at

# **DYNAMIC METRICS**

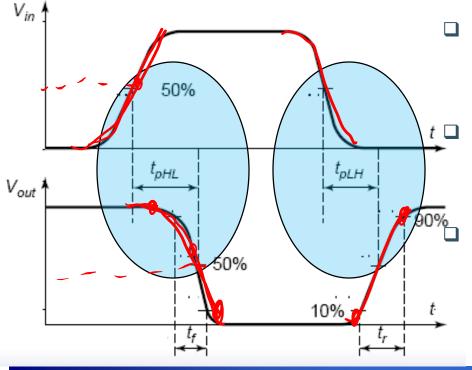

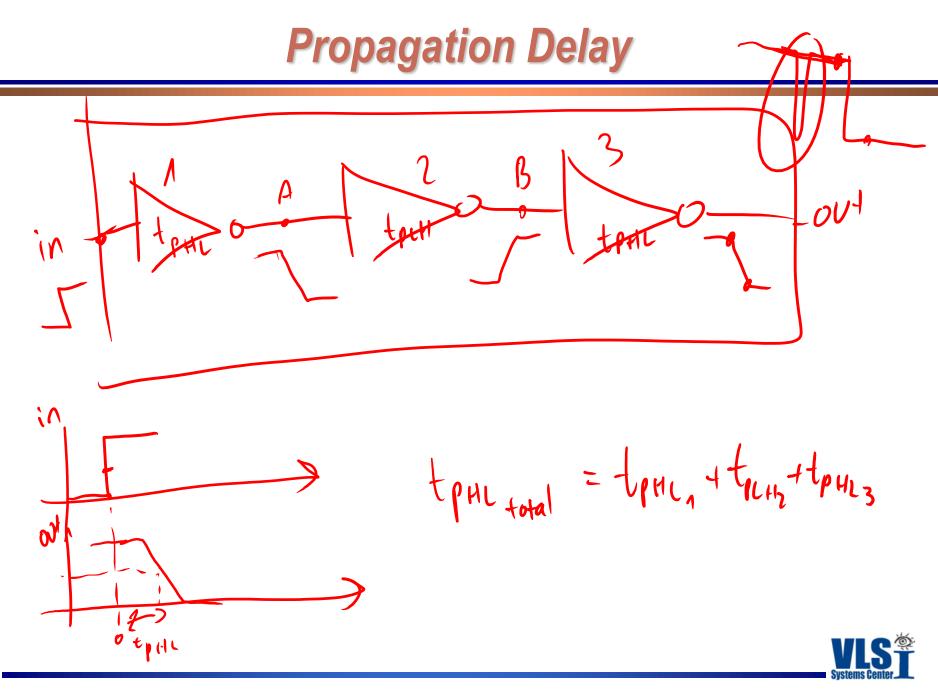

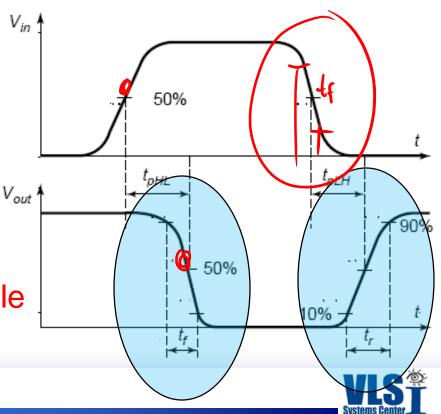

# □ **Propagation Delay** $(t_p, t_{pd}, t_{delay})$ defines how quickly a gate responds to a change in its inputs.

**Propagation Delay**  $f^{> 0}$

» It expresses the delay experienced by a signal when passing through a gate.

- $t_{pd}$  is measured between the 50% transition points of the input and output waveforms.

- There is a separate delay for a *high-to-low* transition  $(t_{pHI})$  and a *low-to-high* transition  $(t_{pLH})$ .

The propagation delay is defined as the average of the two:

$$t_{pd} = \frac{t_{pLH} + t_{pHL}}{2}$$

The VLSI Systems Center - BGU

- □ The *Propagation Delay* depends on the slope of the input and output signals.

- □ To quantify these properties, we introduce *Rise Time* and *Fall Time*.

- □ *Rise Time*  $(t_r)$  is the time it takes a signal to rise from 10% to 90% of its full level.

- □ *Fall Time*  $(t_f)$  is the time it takes a signal to fall from 90% to 10% of its full level.

- □  $t_r$  and  $t_f$  are measured on a single signal, while  $t_{pd}$  is measured between the input and output

### **Rise Time, Fall Time**

**Digital Microelectronic Circuits**

The VLSI Systems Center - BGU

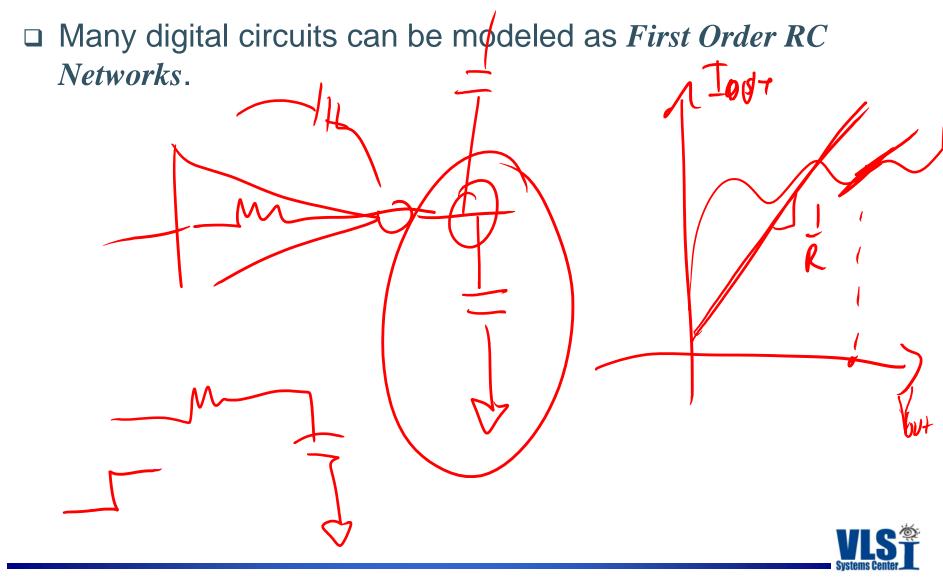

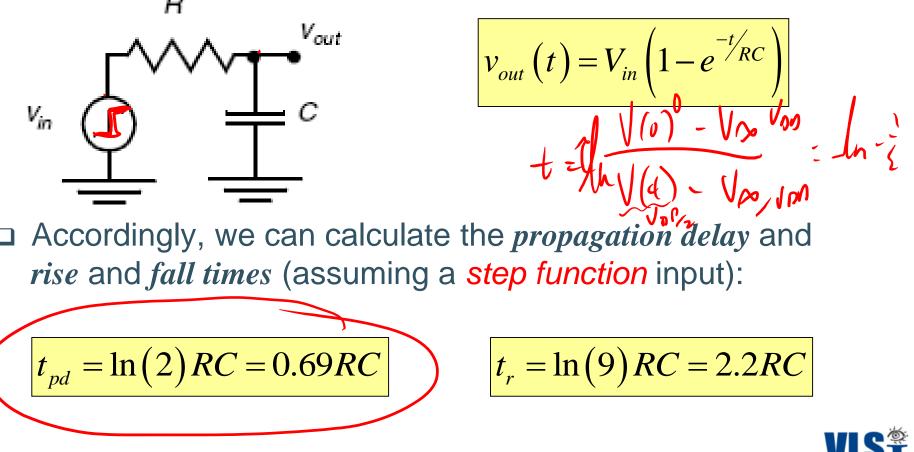

## **Delay of a first order RC Network**

## **Delay of a first order RC Network**

It can be very useful to calculate the *transient response* of this network with a *step input* applied.

Your iPod's battery died again? Let's talk about

# **POWER AND ENERGY CONSUMPTION**

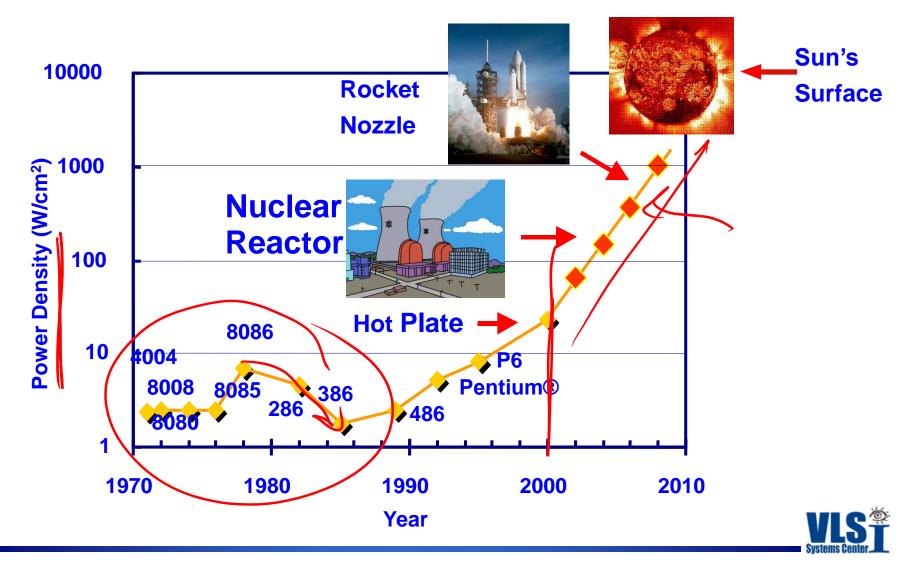

Power Consumption determines how much energy is consumed by the circuit and how much heat the circuit dissipates.

» The rate at which energy is taken from the power source and converted into heat.

□ Several design decisions are influenced, such as:

- » Power Supply Capacity

- » Battery Lifetime

- » Packaging

- » Cooling Requirements

### Therefore, power is a large factor in *feasibility*, cost and reliability.

### **Power Consumption**

Source: Intel

**Digital Microelectronic Circuits**

The VLSI Systems Center - BGU

# **Power Consumption**

#### Power dissipation is a limiting factor in many systems

- » Battery weight and life for portable devices

- » Packaging and cooling costs

- » Case temperature for laptop

- » Fan noise not acceptable in some settings

### Internet data center, ~8,000 servers, ~2MW

- » 25% of running cost is in electricity supply for supplying power and running air-conditioning to remove heat

- Environmental concerns

- » ~2005, 1 billion PCs, 100W each => 100 GW

- » 100 GW = 40 Hoover Dams

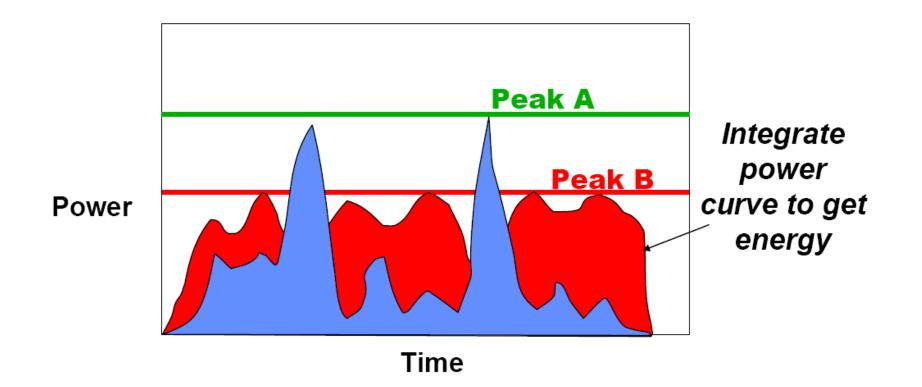

□ The two main metrics of power are *peak power* and *average power*.

» Peak Power (P<sub>peak</sub>) is the maximum instantaneous power dissipated in the circuit:

$$P_{peak} = i_{peak} V_{supply} = \max\left[p(t)\right]$$

» Average Power ( $P_{av}$ ) is the average power dissipated over the interval [0,T]:

$$P_{av} = \frac{1}{T} \int_0^T p(t) dt = \frac{V_{supply}}{T} \int_0^T i_{supply}(t) dt$$

□ The average power can be decomposed into *Static* and *Dynamic Power Dissipation*.

» *Static Power* is the power consumed while the circuit is in its steady state and isn't switching.

$$P_{static} = I_{static} V_{supply}$$

» Dynamic Power is the power consumed during switching.

### **Power of a first order RC Network**

□ Again, we will consider a *First Order RC Network* for generalization of *Dynamic Power Consumption*.

$$E_{in} = \int_0^\infty i_{in}(t) v_{in}(t) dt = V \int_0^\infty C \frac{dv_{out}}{dt} dt$$

$$= CV \int_0^V dV_{out} = CV^2$$

This is the energy consumed for a single transition.

For a given frequency, *f*, we get average dynamic power of:

$$P_{dynamic} = \int C V_0^2$$

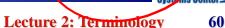

### **Power vs. Energy**

### **Power vs. Energy**

System A has higher peak power, but lower total energy

System B has lower peak power, but higher total energy

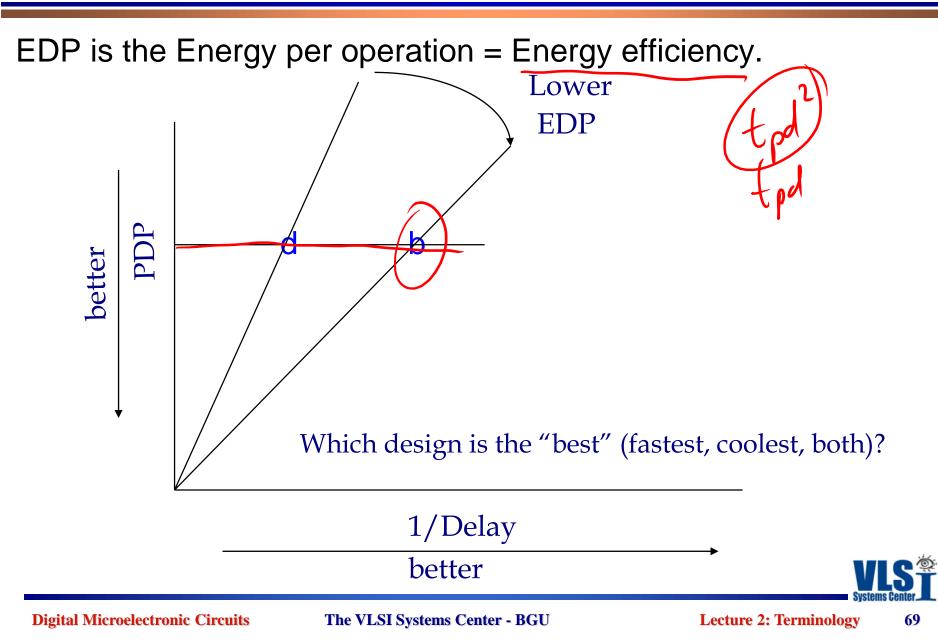

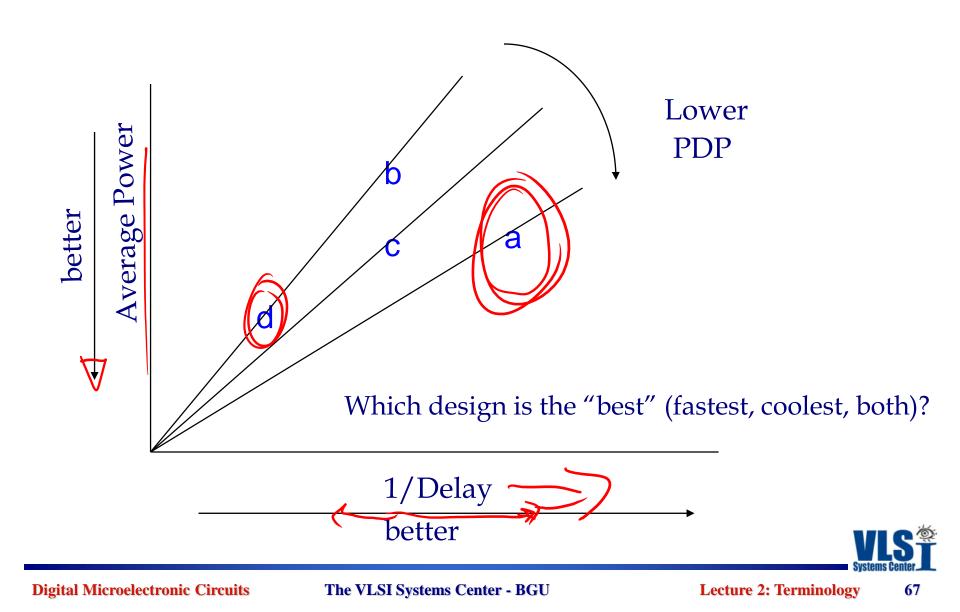

# Understanding Tradeoffs - PDP

# **Understanding Tradeoffs - PDP**

PDP is the energy per switching event.

So just lower the voltage to zero to minimize the energy consumption...

» But then the operation will never finish (and static power will dominate).

$PDP = P_{dynamic} \cdot t_{pd} = \left( \frac{1}{t_{pd}} \right) CV^2 \cdot t_{pd} = CV^2 \cdot (1)^{1/2}$

To take speed into account we will multiply by the delay, giving us *Energy Efficiency*.

$$EDP = PDP \cdot t_{pd} = CV^2 \cdot t_{pd}$$

$P_{dynamic}$

### **Understanding Tradeoffs - EDP**